# tanulmányok 91/1979

MTA Számitástechnikai és Automatizálási Kutató Intézet Budapest

MIKROPROCESSZOROK ÉS MIKROPROCESSZOR-BÁZISU RENDSZEREK ARCHITEKTURÁJA ÉS STRUKTÚRÁJA.

Téli iskola Szentendre, 1978. február 13-18.

ARCHITEKTURE AND STRUCTURE OF MICROPROCESSORS

AND MICROPROCESSOR-BASED SYSTEMS.

Winter School

Előadások Proceeding Доклады

Архитектура и структура микропроцессоров и микропроцессорные системы 3 имняя Школа

#### A kiadásért felelős:

DR VÁMOS TIBOR

Szerkesztette:

DÁVID GÁBOR

ISBN 963 311 078 5 ISSN 0324-2951

Készült a KSH Nemzetközi Számitástechnikai Oktató és Tájékoztató Központ Reprográfiai Üzemében 79/093 A konferenciát a "Számitástechnika tudományos kérdései" c. többoldalu akadémia együttmüködés keretében rendezte a 10. MCS.

Конференция была проведена в рамках многостороннего сотрудничества академий социалистических стран по проблеме "Научные вопросы вычислительной техники"

PM.10.

Conference was held in the frame of the multilateral cooperation of the academies of sciences of the socialist countries on Computer Sciences, WG. 10.

### TARTALOMJEGYZÉK

| SESSION 1: ARCHITECTURE                                                   |

|---------------------------------------------------------------------------|

| F. Vajda: THIS MAKES ME THISNK (UNDER THE PRETEXT OF A WELCOMING ADDRESS) |

| Г. Сальцман: Влияние высокоразвитой микроэлектронной схемой               |

| технологии на создание многопроцессорных систем 17                        |

| J.C. Remesar: MULTILEVEL MEMORY STRUCTURE FOR THE                         |

| CONTROL OF MICROPROGRAMMED MACHINES                                       |

| $E.\Pi.$ Башлаков, М.И. Кратко: Синтез структур микропроцессо-            |

| ров и микропроцессорных систем                                            |

| В. Хенцлер: Стыковка ЭВМ в многомаминных системах на базе                 |

| микро- ЭВМ 61                                                             |

| G. Dávid, S. Keresztély, I. Losonczi, A. Sárközy:                         |

| LOGIC-BASED DESCRIPTION OF MICROCOMPUTERS                                 |

| S. Ebergényi, L. Levelki, G. Nessing, M. Szalay:                          |

| CONSIDERATIONS FOR IMPLEMENTING A MICRO-BASED                             |

| MINICOMPUTER 93                                                           |

| P. Kerntopf: A SURVEY OF TECHNIQUES FOR TESTING                           |

| MICROPROCESSORS                                                           |

| И. Эрени: Методы и средства проектирования цифровых уст-                  |

| ройств, выполненных на базе микропроцессоров 109                          |

| SESSION 2: SYSTEM DEVELOPMENT SYSTEMS                                     |

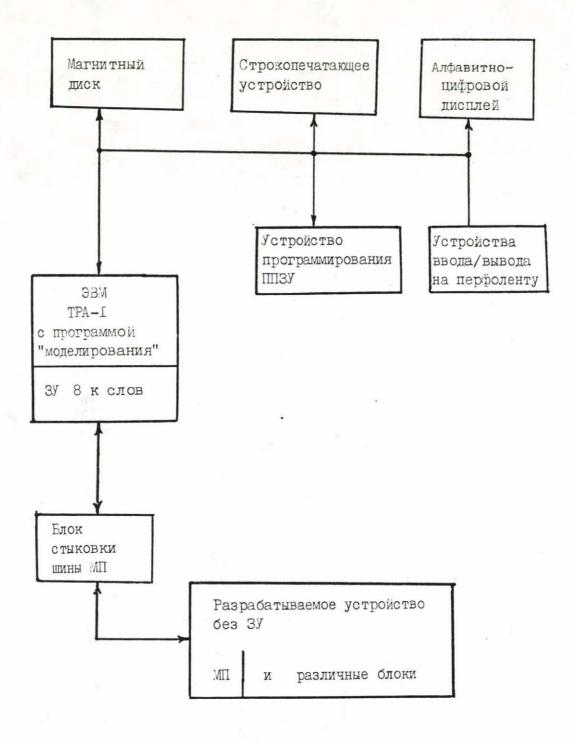

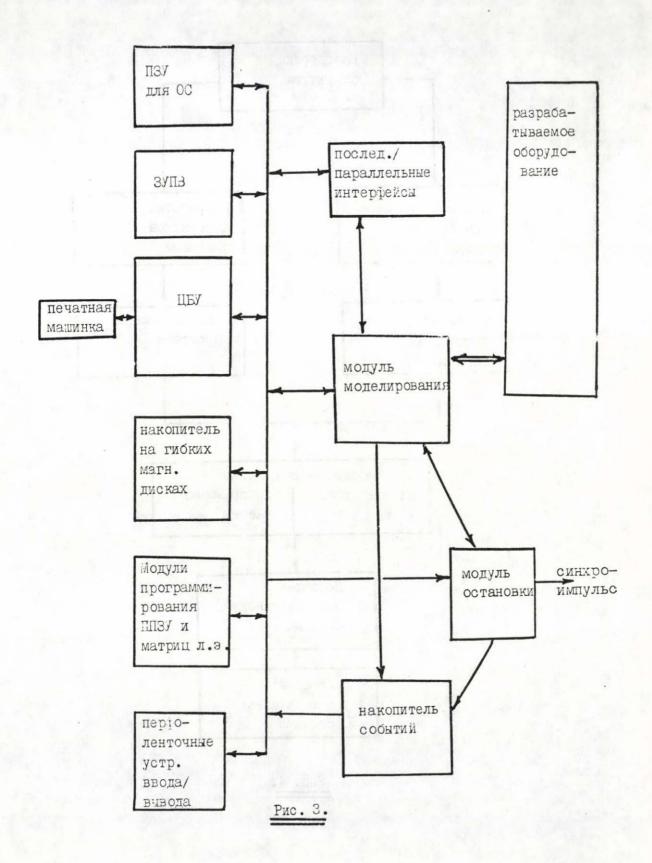

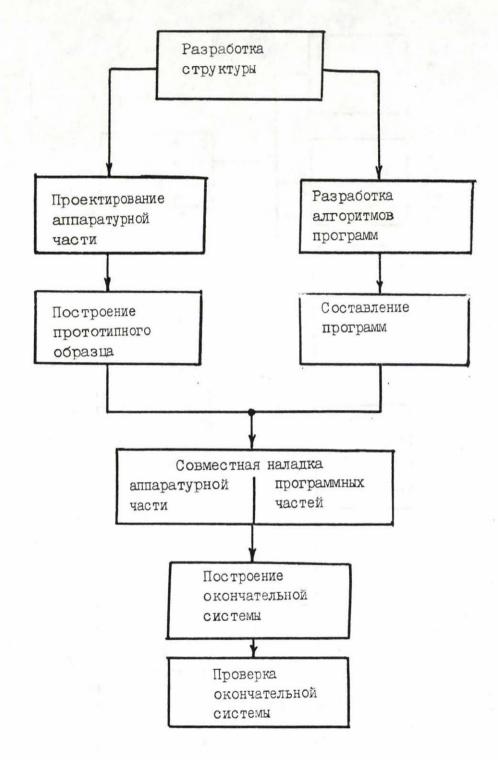

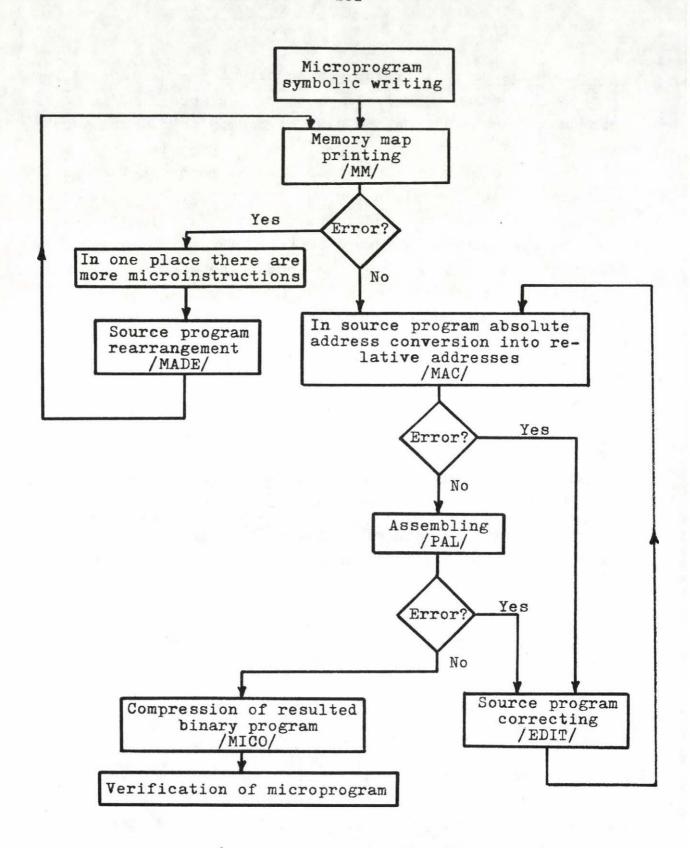

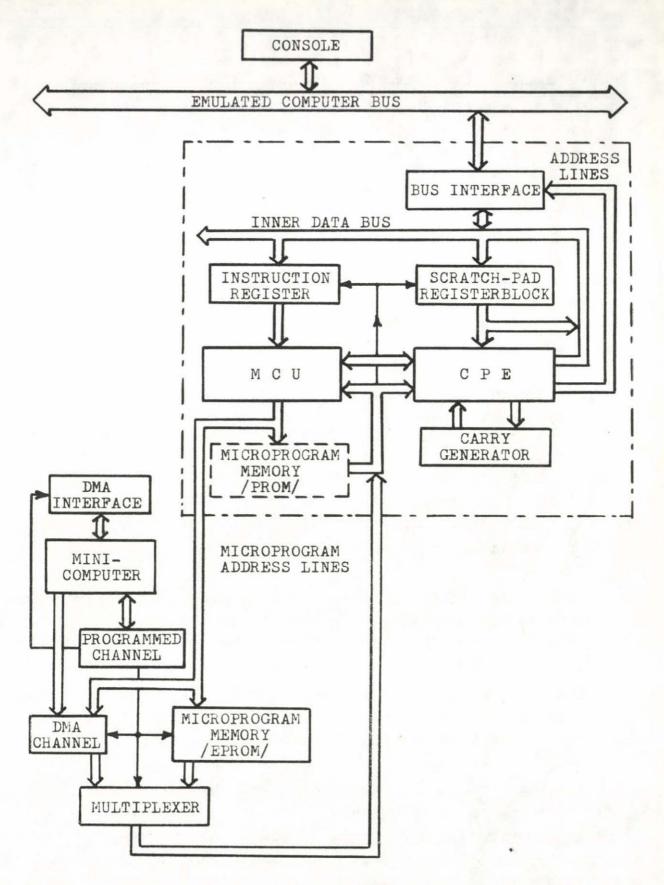

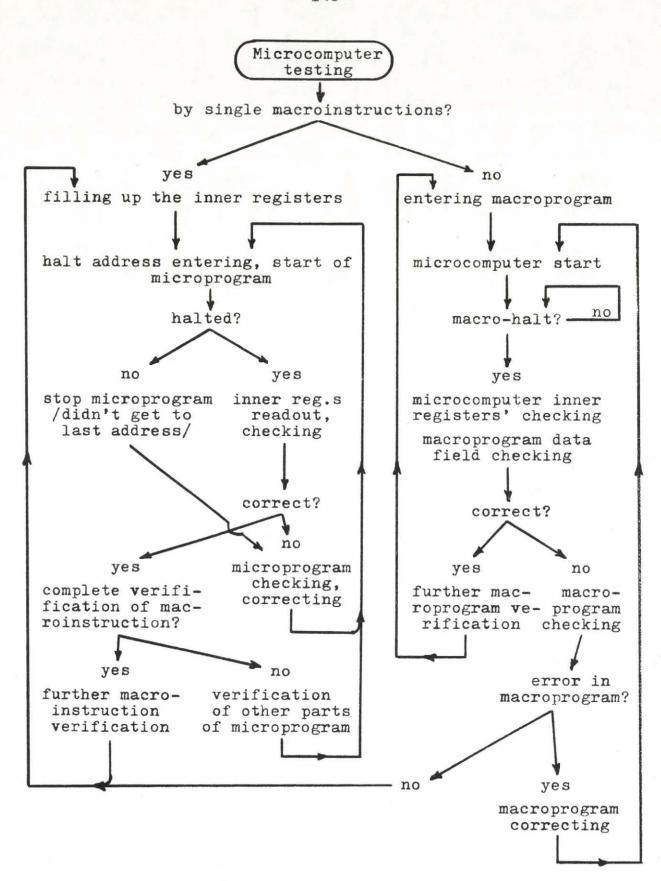

| G. AMBROZY, J. Miskolczi: MICROPROGRAM DEVELOPING                         |

| SYSTEM FOR EMULATION PURPOSES BASED ON A PDP-8E 127                       |

| SESSION 3: SOFTWARE                                                       |

| G. Dávid: PROBLEMS IN MICROPROGRAMMING                                    |

| R.W. Marczynski: MICROPROGRAM STRUCTURES OF                                                  |      |

|----------------------------------------------------------------------------------------------|------|

| MICROPROCESSORS                                                                              | 153  |

| M. Tudruj: MODULAR MICRORPGRAMMING APPROACH                                                  |      |

| IN MICROPROCESSORS                                                                           | 165  |

| G. Dávid, S. Keresztély, I. Losonczi, A. Sárközy:                                            |      |

| MICROPROGRAM SYNTHESIS                                                                       | 187  |

| Б. Хацклер: Симуляция приборо-технических функций вычисл                                     | IN-  |

| тельной системы на базе микропроцессора в реальном масштабе времени. SESSION 4: APPLICATIONS | 207  |

| Р. Шульце: К вопросу оптимизации разделенных по задачам                                      |      |

| многопроцессорных систем.                                                                    | 217  |

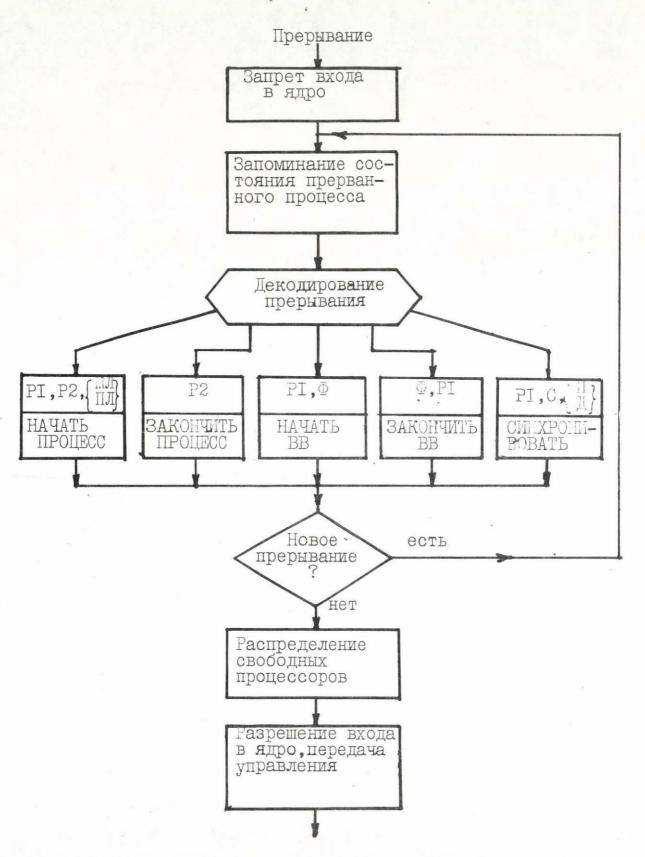

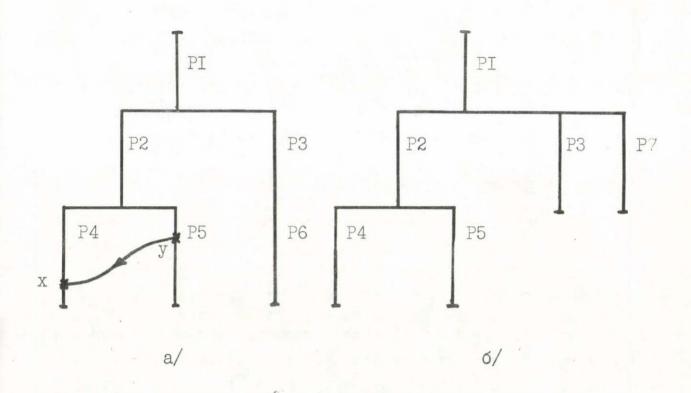

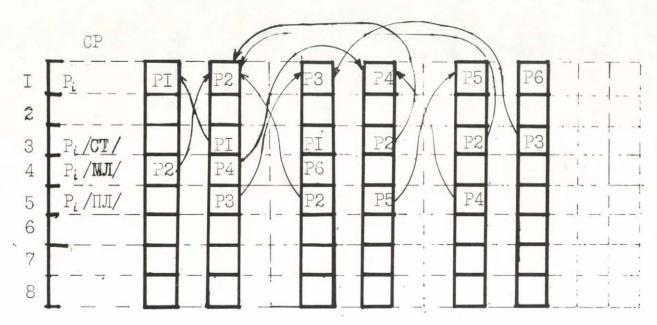

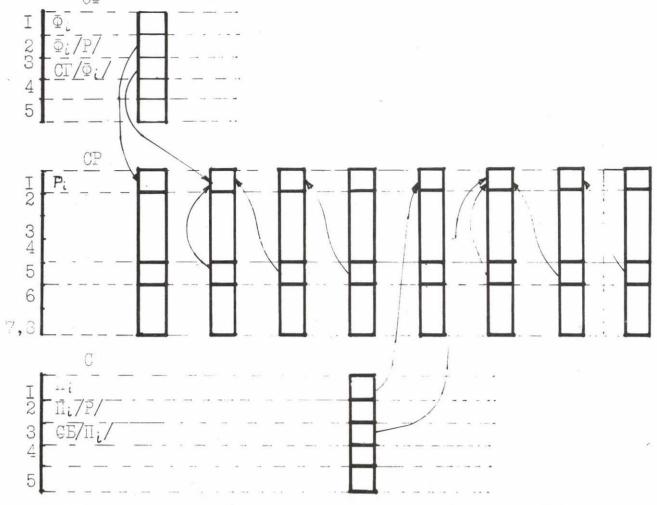

| Г. Хротко: Ядро операционной системы в мультимикропроцес                                     | cop- |

| ной системе.                                                                                 | 233  |

| J. Moudry, L. Jakus: CASSETTE MEMORY FOR DATA                                                |      |

| STORAGE CONTROLLED BY MICROPROCESSOR                                                         | 245  |

SESSION 1: ARCHITECTURE

Сессия 1: Архитектура

### THIS MAKES ME THINK ... (UNDER THE PRETEXT OF A WELCOMING ADDRESS)

#### F. VAJDA

Central Research Institute for Physics of the Hungarian Academy of Sciences, Budapest, Hungary

Having the unusual opportunity of opening this winter school, please allow me to introduce a few thoughts of mine regarding its topics.

The main purpose of our winter school is to facilitate the international flow of information among the participating socialist countries in the field of

- microprogramming and

- microprocessing (in other words: microprocessor applications.)

Our scope of interest includes in particular

- theory

- research

- design

- development

- application

#### relating to

- microprogramming

- microprocessor systems

- distributed computing and multimicroprocessor system

- integrated hardware-firmware-software design.

The main components of up-to-date system design are:

- hardware

- software

- formware

- brainware (We are particularly strong in this field!)

We are to have a separate section of the school devoted to application aids (developing tools and methods); because there is no system development without a development system. We have to change today's situation when microprocessor programming is like printing before Gutenberg.

First of all a few definitions are shown to have a "common vocabulary".

A microprocessor is the central processing unit of a small computer implemented on one or a few LSI chips.

The computer based on a microprocessor is a microcomputer.

Microprogramming is the design of the control function of a processing system as a sequence of control signals which are organized into words (called microinstructions) and stored in a control memory.

A system is microprogrammed if this control function is implemented in this way and microprogrammable if the control function can be changed by the user.

An emulator is a microprogrammed system which copies another system.

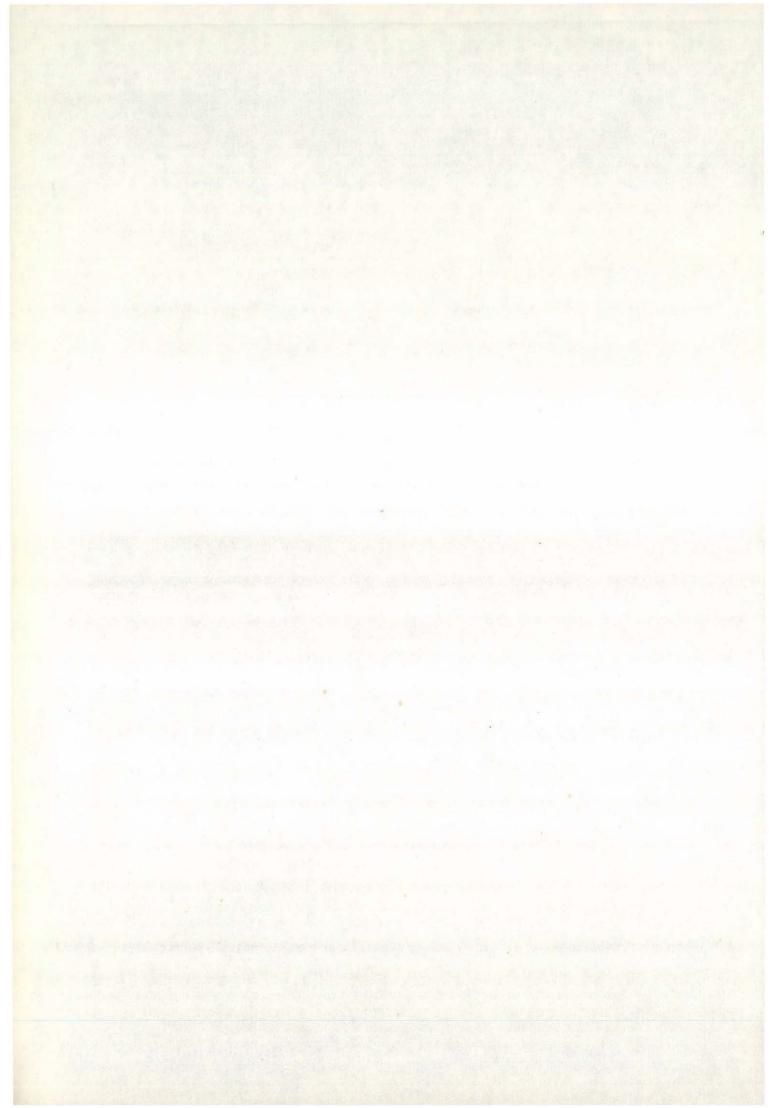

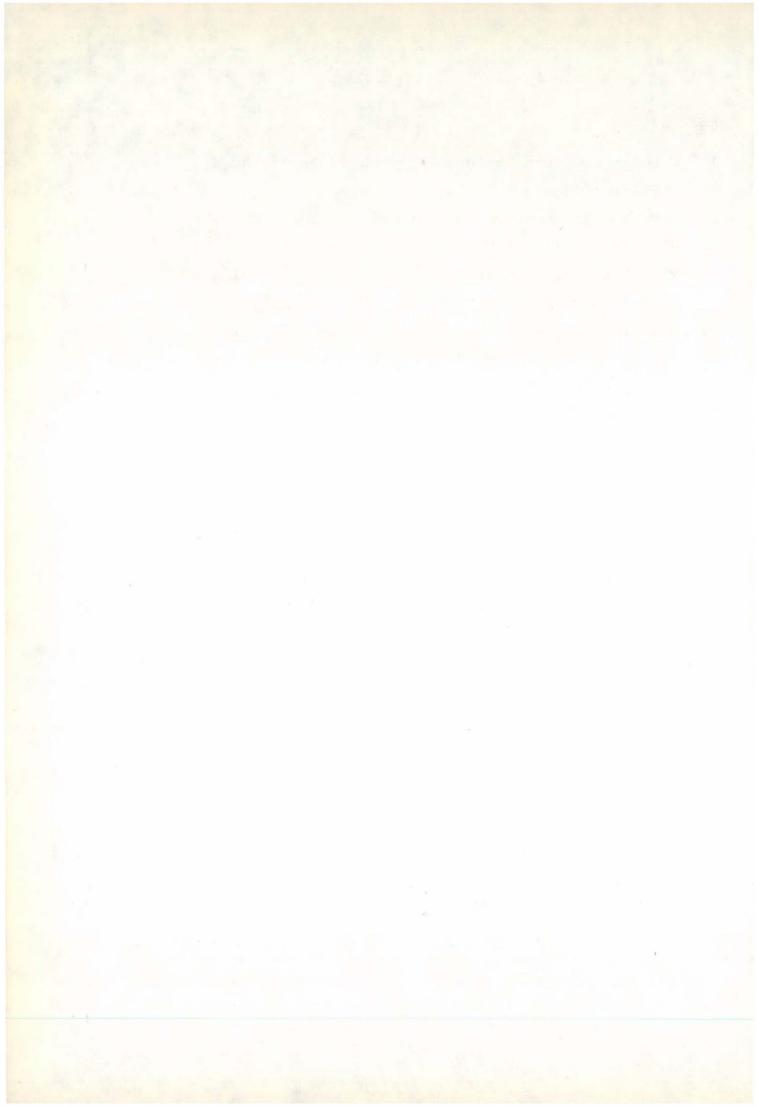

Considering components' development, Texas Instruments VLSI (Very Large Scale Integration) schedule is given in Fig. 1.

Fig. 1.

Texas Instruments VLSI schedule.

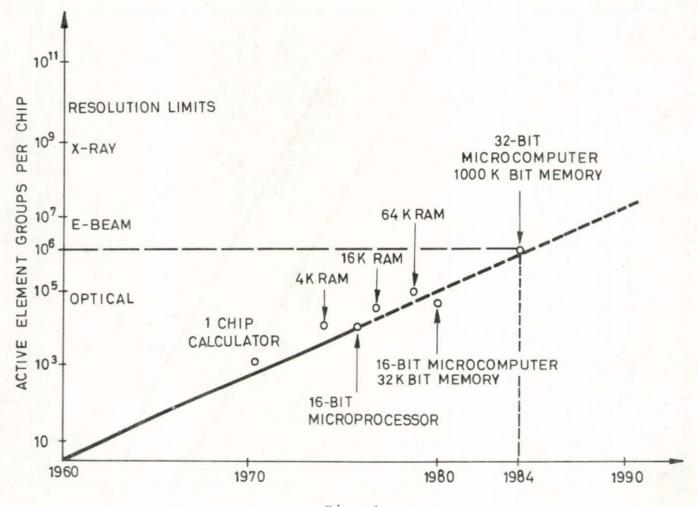

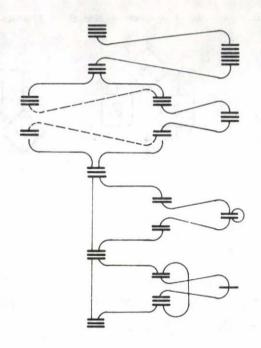

Regarding VLSI "mathematics", the general rules are as follows (see Fig.2.)

- Number of elements doubles every year (The so called "Moore-Nayce rule")

- Chip size increases slowly with time; therefore, element size must decrease.

- Chip power dissipation must remain constant; therefore, dissipation per element must be halved every year.

rig. Z.

VLSI "mathematics".

Considering now the two main topics i.e. microprocessors and microprogramming and the *interaction between them* we find that the greatest impact of microprocessors on microprogramming so far is in the implementation if microprogrammed systems with bit-sliced microprocessors.

In the field of bit-sliced processor applications the most important areas of interest are:

- Emulation of existing minicomputers (e.g. NOVA, PDP-11, Intel 8080, Interdata 7/16 etc.)

Difficulties in implementation:

- Complex bus Structure

- I/O systems

- High speed controllers for

- process control systems

- video displays

- communication etc.

A microprogrammed system without arithmetic capability oriented toward control applications is called a micro-controller. An LSI sequencer together with a microprogram memory and some other elements may do the job alone.

- Special-purpose computing elements. The current and potential applications are as follows.

- Signal processing, e.g. filtering, transformation, statistical analysis etc.

- Simulation, e.g. direct execution of simulation languages.

- Video processing.

There is a new tendency in microprogrammable universal computersthe so-called flexible architecture (e.g. Nanodata Q-1 with many independent buses which can be configurated in order to meet particular needs). This tendency leads to a new category and brought to life the universal host as a research and development tool. We shall refer to its application as emulative support. The applications of a universal host computer by the manufacturer can be

- in the development of new microprocessors.

The manufacturer could easily experiment with different architectures, design instruction sets, and emulate existing machines. It is a flexible hardware and software tool.

- Developing new I/O chips to be used with microprocessors.

In many cases the latest chips are even more complex than the processors with which they work. These chips themselves may be microprogrammed. Therefore the universal host could be a tool in the design of such chips - as programmable interfaces, single--chip peripheral controllers - and could support their microprogramming.

- Developing System Software for microprocessors.

In this case the system software could be written using the universal host and would not depend on the availability or performance of the processor itself.

Application of the universal host computer by the user:

Advantages are the same as for the manufactures, among other things these are experimentation with different architectures and instruction sets, rapid development of software and emulation of existing machines. The user of microprogrammable processors can develop microprograms and essential system software on the universal host. It can be used as a single development tool for many different processors and can benchmark different devices. It is very useful for the development and design of custom LSI.

There is also a new offspring of merging hardware and software, the SSS (Solid State Software). This is a new methodology for developing reliable and efficient application programs for microprocessors. It means low cost, off-the-shelf operational

and support software in ROMS. Operational subroutines are eqvivalent to LSI building blocks. They reduce the programmers burden, requiring only linking modules. Today's microprocessor architectures contain an important feature that has a strong impact on this design strategy. This feature is an external address stack which is managed in hardware, via a stack pointer register and the CALL and RETURN instructions within the processor's instruction set. Use of the stack for program results in a lot of work being performed at a reasonably low price.

Finally, dealing only very shortly with the many possible consequences of using microprocessors, we refer to Fig.3 which covers a wide range of overlapping areas affecting individuals and society.

I am very pleased to velcome you here in Szentendre and wish you a successful and pleasant time both on my behalf and on the behalf of the organizing committee.

#### REFERENCES

- M. Layer: Microprocessors, side effects and society. Microprocessors, 1/1977/ pp. 305-308.

- M.A. Boden: Social implications of intelligent machines

The Radio and Eelctronic Engineer, 47/1977/ pp.393-399.

- 3. T.P. Hughes at al.: LSI software. Microcomputers'77 Conf. Record /Oklame City, 6-8 April 1977/ IEEE New York, 1977. pp. 46-53.

- H. Schmid: Monolitic Processing Overview /Privat communications/.

ВЛИЯНИЕ ВЫСОКОРАЗВИТОЙ МИКРОЭЛЕКТРОННОЙ СХЕМНОЙ ТЕХНОЛОГИИ НА СОЗДАНИЕ МНОГОПРОЦЕССОРНЫХ СИСТЕМ

#### Г. Сальиманн

НП Роботрон, научно-исследовательский центр

Прогрессивное развитие микроэлектронной схемной технологии в связи с новыми потребностями и привычками пользователя существенно может влиять на будущие поколения ЭВМ. Использование больших интегральных схем /БИС/ требует модульной организации функций системы и приводит к новым принципам проектирования. При этом многопроцессорные и многомашинные системы на базе микропроцессоров могут играть большую роль. Настоящий уровень характеризуется концепцией и опробованием ряда новых решений, в результате которых стандартное решение до сих пор не могло быть получено. На основе еще решаемых вопросов, включая вопрос обеспечения совместимости с существующей вычислительной техникой в эксплуатации, краткосрочных принципиальных изменений в области универсально используемых ЭВМ средней и высокой производительностью не ожидается.

#### 1. Введение

С возможностью использования микроэлектронной схемой технологии, позволяющей очень высокую степень интеграции и низкие затраты на элемент, за минувшие годы начал процесс, который в будущем, быть может, рассматривается как качественно новый этап в области реализации и использования техничес-

ких средств ЭВМ. Как показывается, микроэлектроника не только оказывает воздействие на дальнейший научно-технический прогресс в народном хозяйстве, но она также будет влиять на общественное развитие.

Одно направление этого процесса уже ясно вырисовывается. Все в большем объеме находят применение мини ЭВМ и технические средства ЭВМ в совершенно новых сферах, как например, в устройствах децентрализованного управления и обработки для множества устройств и оборудований, включая потребительские товары.

Менее очевидными, однако, являются возможные воздействия на традиционные классы универсальных малых и больших ЭВМ. Считается, что использование больших интегральных схем в этой сфере также может приобрести большое значение. Для рассмотрения возможных направлений развития вычислительной техники мы считаем такую исходную точку особенно пригодной, причем другие коэффициенты влияния не остаются без внимания.

#### 2. О развитии схемной технологии

Настоящее состояние развития БИСов по п-МОП-технологии характеризуется степенью интеграции 10.000 ÷ 20.000 транзисторов/чип. Это позволяет, что в одну схему могут быть включены 8-разрядный микропроцессор с высокой производительностью и тактовой частотой более 2 Мгц., память 8 Кбит или 16 Кбит или даже микро-ЭВМ с центральным процессором, входные и выходные каналы и некоторая память для 8-разрядной обработки. Международно предполагается, что теперешнее развитие постоянного повышения степени интеграции за счет совершенствования технологий и повышения скорости переключения, уменьшения потребления мощности и стоимости будут продолжаться. При этом большую роль будет играть переход к новым методам структурирования. Используемый в настоящее время метод фотолитографии позволяет изготовление структурных элементов шириной прибли-

зительно 1 мкм. Это является границей, установленной длиной световых волн. С применением электроннолучевой литографии расчитывают получить не менее десятикратного меньшего значения. На основе более новых прогнозов /2/ для развития степени интеграции выделяются следующие этапы:

| Сроки   | Степень интеграции<br>транзисторы/чип | Параметры схемы                                                                |

|---------|---------------------------------------|--------------------------------------------------------------------------------|

| 1976/77 | 1 ÷ 2 x 10 <sup>4</sup>               | 8-разрядный центральный процессор или 8-разряд-<br>ная микро-ЭВМ на одном чипе |

| 1979    | 10 <sup>5</sup>                       | 16-разрядный центральный процессор с памятью и входными и выходными ка-        |

| 1984    | 10 <sup>6</sup>                       | 32-разрядный центральный процессор с памятью 64 Кбит.                          |

На основе процесса бывшего развития микроэлектроники нет повода для игнорирования таких прогнозов. Уже теперь имеются в распоряжении 16-разрядные микропроцессоры или 16-разрядные ЭВМ на одном чипе; получено сообщение о появлении на рынке дальнейших процессоров /4/, /5/. Целью является достижение производительности процессора, отвечающей производительности типа PDP 11 серии 40. Здесь поднимается принципиальный вопрос о том, как использовать эти технологические возможности для средней и высокой техники и для универсальных машин.

#### 3. Некоторые вопросы проектирования ЭВМ на базе БИСов

Специфика БИСов требует некоторых новых предпосылок для

проектирования процессоров, тесно связанных с требованиями пользователя к новым системам. Существенным влиянием на стратегию проектирования и создание новых структур и архитектур являются следующие аспекты:

1. С одной стороны, современная полупроводниковая техника позволяет высокую и все больше повышающуюся степень интеграции. С другой стороны, число внешних присоединений, т.е., число вводов сигналов в интегральную систему из-за технологических причин очень ограничивается, в настоящее время - на 40 ÷ 70. В связи с этим, только те функциональные единицы /блоки/ интегрируемы, которые доступны в кодированном виде по малому числу сигнальных проводов.

Эти условия требуют модульной организации ЭВМ, разделенной, по возможности, на законченные субкомплексы. Такими функциональными комплексами, например, являются процессоры /с системной программой/, модули памяти или логические блоки интерфейса, коммуникация которых должна проводиться с помощью соединительной системы. Таким образом, специфика техники БИС приводитк созданию многопроцессорных систем с возможностью лучшей деконцентрации функций системы. С точки зрения эксплуатации, этим даны предпосылки улучшения прозрачности системы и достижения более высокой гибкости при приспособлении /адаптации/ к задачам, а также расширяемости за счет переоснащения.

2. С увеличивающейся степенью интеграции повышается комплектность /сложность / схемы с тенденцией специализации. Повышаются основные затраты на проектирование и разработку схемы и уменьшается количество изделий на единицу устройств. В экстремальном случае все основные функции ЭВМ могут быть размещены на одном чипе. Поскольку речь не идет об использовании схем крупных серий, выводом из этого является задача оптимизации с целью достижения соответствующей степени универсальности набора схем. На основе малого, по возможности, числа типов схем следует обеспечить экономичное производство схем в больших количествах.

Это противоречие между тенденцией специализации и требованиями универсальности также приводит к модульной организации функций системы с названными в п. 1 последствиями, причем различные функции могут быть реализованы соответствующим программированием аппаратных модулей, т.е. процессоров.

3. Экономичное производство БИСов /массовое производство функциональных элементов в одном процессе/ уже сегодня обеспечивает малые затраты на одну логическую функцию.

Путем лучшего освоения технологии и повышения плотности функций эти затраты все больше уменьшаются. Из этого вытекает экономическая необходимость использования БИСы, изготовляемые с помощью таких технологических процессов или технологий, которые требуют малого количества производственных шагов /операций и позволяющих высокую плотность упаковки. Одновременно изменяются пропорции затрат между компонентами вычислительной системы и этим - действительные до сих пор принципы проектирования. В связи с тем, что имеется достаточная дешевая мощность ЭВМ, ее максимальное пользование все же не стоит на переднем плане. Однако необходимым является обеспечивать наилучшее использование остальных ресурсов системы /накопителей, периферий/ и уменьшить затраты на разработку системных программ. Эти аспекты также способствуют созданию многопроцессорных структур за счет использования относительно дорогих ресурсов системы некоторыми процессорами.

Схемная база, требующая меньших затрат, является предпосылкой все большей работы с резервом, а также уменьшить объем и степень сложности машинно-ориентированного матобеспечения. Возможности для этого вытекают из уменьшения организационных затрат внутри системы, из децентрализации и из перевода функций системы, исполнение которых до сих пор преимущественно блоки /модули/ с программируемой памятью. Это, однако, требует организации многопроцессорного режима на основе новых программых средств.

С точки зрения эксплуатации, экономия схемотехники на базе БИСов приводит к улучшению соотношения производительность/ цена и открывает возможные пути к системам, допускающим отказы, а также к лучшему обслуживанию ЭВМ, например, за счет широкого использования средств коммуникации и использования языков программирования более высокого уровня.

Этим мы констатируем развитие условий, взаимодействующих на изменение архитектуры и структуры ЭВМ. Наряду с эксплуатационными /пользовательскими/ требованиями значительное влияние, преимущественно, имеют технологические возможности в связи с экономическими факторами.

- 4. Некоторые возможности использования многопроцессорных и многомащинных структур на базе микропроцессоров

- 4.1. Повышение производительности и ее приспособление в организации параллельной работы

Организация параллельной работы некоторых процессоров позволяет, при наличии соответствующей схемной базы и данной границы затрат, повысить производительность системы по сравнению с однопроцессорной системой, или за счет соответствующей конфигурации приспособить ее к требованиям пользователя.

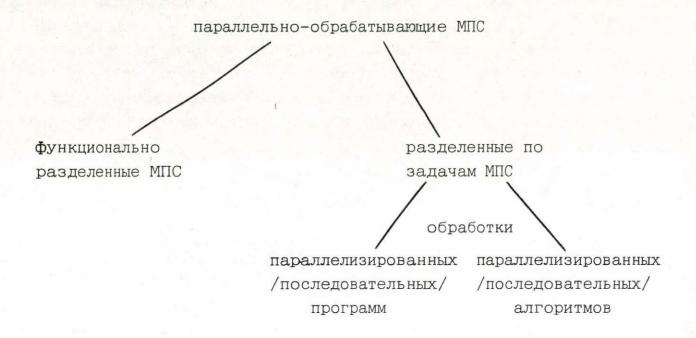

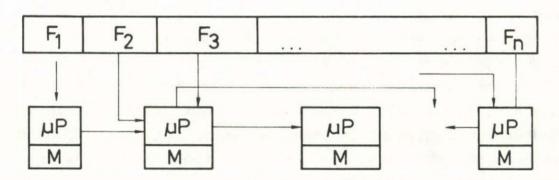

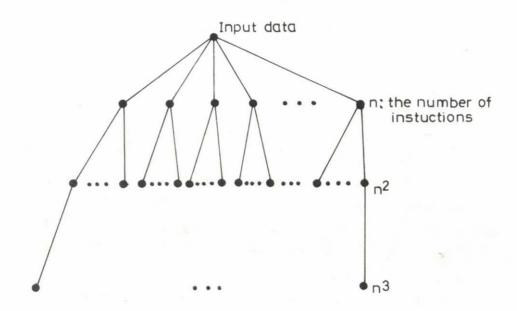

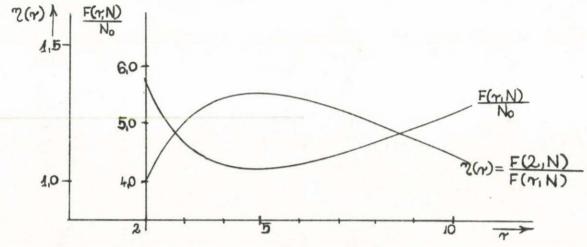

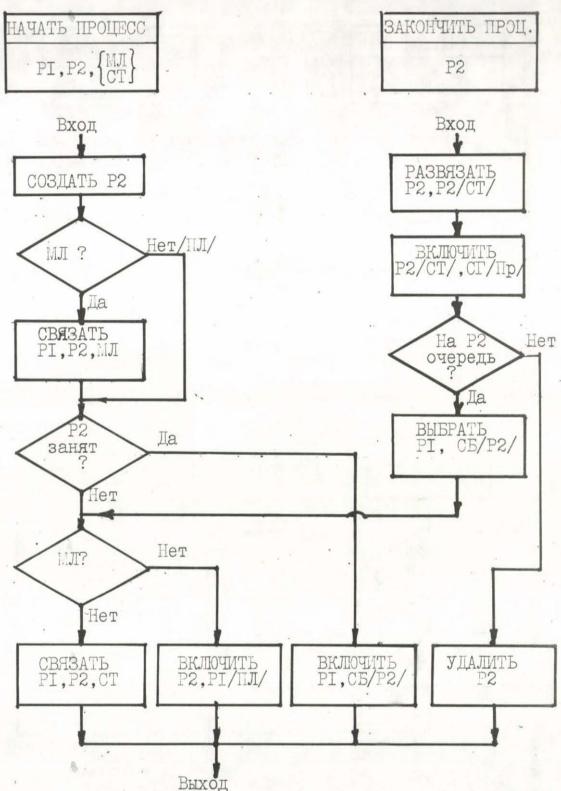

Целесообразной является классификация по функциям и задачам /см. рис. 1/, хотя здесь не во всяком случае достигается ясное ограничение.

В случае функционально-разделенных систем проводится специализация функций системы на некоторых процессорах, сохраняя режим последовательной обработки команд. В связи с тем, что в настоящее время программы разрабатываются, преимущественно, для последовательной обработки, такие системы могут использоваться универсально. Например, может быть проведено разделение работ между процессорами для управления, обработки, вво-

да/вывода, технического обслуживания и диагностики.

В случае разделенных на задачи систем организуется параллельная /одновременная/ обработка последовательного параллелизованного алгоритма или программы на некоторых процессорах с целью повышения пропускной способности системы. Универсальное использование таких структур связано с автоматическим разделением программы на параллельно обрабатываемые секции на этапе компиляции. Для специальных случаев применения /например, в области управления технологическими процессами/ параллельная работа организуется программистом или структура системы прямо выводится из алгоритма решения одного класса проблем /например, для задач вычислительной математики/.

На практике по функциям и по задачам не редко проводится в смешанном виде.

#### 4.2. Системы допускающие отказы

Многомикропроцессорные структуры также могут являться основой реализации систем, допускающих отказы, необходимые в случае высоких требований к надежности. Эти структуры с "мяг-ким поведением отказа" представляют собой экономическую альтернативу к двойным и тройным системам. Соответствующая модульная организация системных функций, аппаратные и программые средства и упорядочивание приоритета в связи с эффективными мерами диагностики позволяют в случае неисправности сохранение работоспособности системы, в необходимом случае также с пониженной производительностью.

#### 4.3. Децентрализованная обработка

Для различных случаев применения, например, для терминалов или комплексов цифрового управления, типичными являются относительно автономные подсистемы, связанные с ведущей ЭВМ. С целью упрощения организации системы, ограничения затрат на аппаратуру /линии/ передачи информации и повышения надежности системы возможным является переводить некоторые процессы обработки на подсистемы. Экономической основой для этого также являются дешевые микропроцессоры. В связи с тем, что управляемые ведущей ЭВМ интеллектуальные подсистемы только "слабо" соединены друг с другом, такой комплекс может считаться многомашынной системой.

#### 4.4. Состояние в настоящем

Использование многопроцессорных систем и соединение малых и больших ЭВМ для создания многомашинных комплексов в области электронной обработки данных не являются новостью.

В международных масштабах, однако, за минувшие годы в возрастающей степени были спроектированы и опробованы системы на базе микропроцессоров во многих вариантах. Они, преимущественно, служат для исследования принципов решения и частичных проблем; коммерческого значения, однако, эти системы до сих пор не могли приобрести.

Несмотря на то, что определенные элементы уже используются, как например,

- шина, работающая с разделением времени как соединительная система;

- коммуникация через общую память для быстродействующего обмена данными;

- относящиеся к процессорам накопители для разгрузки шины и сокращения времени ожидания BM;

- принцип "мастер-слейв" /Master-Slave/ для проведения обмена данными,

стандартные решения для многопроцессорных систем до сих пор не были получены.

В случае системы "слабого или нежесткого" соединения ситуация немного другая. На рынке появились первые изделия,

предназначенные для режима "мастер-слейв" /5/.

При оценке данной ситуации следует учесть, что широкое введение новых архитектур ЭВМ для универсального использования также предполагает обеспечение совместимости с существующим поколением /генерацией/, по крайней мере на уровне прикладных программ. В связи с этим следует отметить, что теоретических основ, вспомогательных средств и эмпирических данных для проектирования многопроцессорных систем, в особенности для определенных целей использования, еще мало. Это касается почти всех частичных проблем, как

- проектирования и оптимизации архитектуры и структуры;

- моделирования, описания системы и имитации;

- модульной организации, специализации функций на функционально разделенные системы и конфигурации интерфейса;

- сети связи;

- операционных систем;

- разделения программы на параллельно обрабатываемые секции; языков программирования, поддерживающих параллельную обработку;

- динамического структурирования, самодиагностики и реконфигурации;

- использования аппаратных средств для уменьшения объема и сложности машинно-ориентированного матобеспечения;

- прямой интерпретации языков более высокого уровня;

- обеспечения совместимости;

- оценки производительности и эффективности;

- создания наборов БИС для многопроцессорного и многомашинного режима.

Эта ситуация требует интуитивного и широкого ориентиро-ванного на проблему подхода. Для того, чтобы полностью использовать все возможности высокоразвитой микроэлектронной схемой технологии для перспективной вычислительной техники, надо еще решать ряд научно-исследовательских задач.

Рис. 1.: Классификация многопроцессорных систем /МПС/

#### ЛИТЕРАТУРА:

- /1/ Grimes, J.D.: Microprocessors and Microcomputers.

Selected reprints from Computer. IEEE Computer

Society 1977.

- /2/ IBM 370 on a Chip in 1984. Electronics Weekly, London /1977/ Nr. 893, p. 2.

- /3/ Köhler, E.: Entwicklungsbestimmende Faktoren für die Halbleitertechnik und Mikroelektronik nach 1980. Sozialistische Rationalisierung in der Elektrotechnik/Elektronik Berlin 6 /1977/ 7, p. 176-178.

- /4/ Osborne, A.: 16-bit-Mikroprozessoren erobern den Minicomputermarkt. Elektronik, München, 26 /1977/10, p. 16.

- /5/ Klasche, G.: Notizen aus den USA. Elektronik, München, 26 /1977/ 9, p. 81-88.

- /6/ Köhler, R.: Computer der 70er Jahre. Elektronik, München, 24 /1975/ 1, p. 75-79.

- /7/ Enslow, P.H.: Multiprocessors and Parallel Processing. John Wiley and Sons, New York, 1974.

- /8/ Reyling, G.: Performance and Control of Multiple Microprocessor Systems. Computer Design, Winchester Ma, 13 /1974/ 3, P. 81-86.

- /9/ Weissberger, A.J.: Analysis of Multiple Microprocessor System and Architectures. Computer Design Winchester Ma, 16 /1977/ 6, p. 151-163.

- /10/ Turn, R.: Computers in the 1980s-Trends in Hardware

Technology. Information Processing 74, North-Holland

Publishing Company, 1974 p. 137-140.

- /11/ Merkel, G.: Zur Architektur elektronischer Rechenanlagen.

Beiträge zur Informationsverarbeitung, Schriftenreihe

Informationsverarbeitung BSB B.G. Teubner Verlagsgesellschaft, Leipzig, 1977, p. 77-89.

## MULTILEVEL MEMORY STRUCTURE FOR THE CONTROL OF MICROPROGRAMMED MACHINES

J.C. REMESAR

Cuba

#### ABSTRACT

This paper proposes a multilevel the organization of the control memory in microprogrammed computers. The fundamental achievement is the flexibility obtained in programming a system with such architecture. User's language development is done via microprogramming. Only a simple assembler could allow the programmer to employ high and low-level instructions in his work. This architecture presents good characteristics for special-purpose microprocessor-based system design.

#### INTRODUCTION

Microprocessor revolution has played a decisive role in the growth of software/hardware costs ratio. Because of this people are paying more attention to those problems traditionally solved by software, which could be simplified by hardware.

Microprocessor-based systems are very often used for special-purpose equipment design, but when programs to be developed

for them present some complexity, the low price components

achievement could be lost because of software development costs.

There are two alternatives:

- to code large programs in machine language

- to develop basic software means as assemblers, macro-assemblers, compilers, stc.

The architecture presented allows the solving of user-oriented language creation via firmware.

#### SOME FUNDAMENTAL TOPICS IM MICROPROGRAMMING

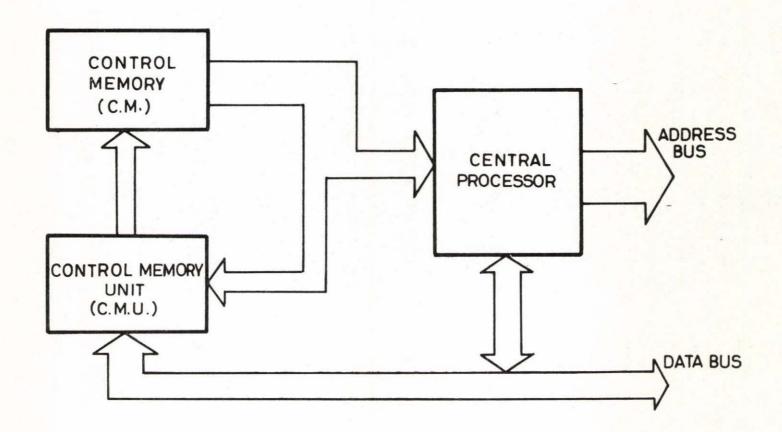

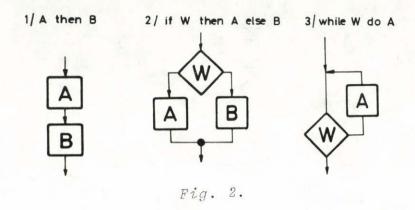

The general principles upos which Wilkes based his work (1), and the development of them until today (2, 3, 4) might be summarised as - follows, using fig 1:

- it is a processor whose control is governed by a set of lines called the "Control bus"

- it is a control memory (CM), loaded with a binary number at each of its words in such a way that every one corresponds to a certain microinstruction (MI) code of the processor

- the microinstruction set of any processor is determined during its design, and the instruction set of the computer is developed by programming the CM. On this rests the flexibility of microprogrammed machines.

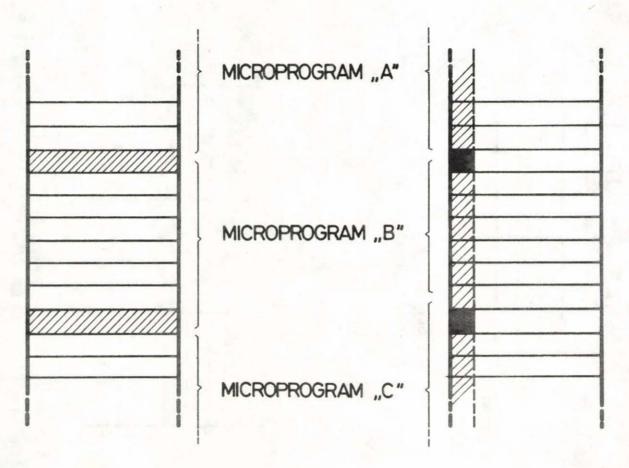

To recognize the end of each microprogram (MP), and consequently the end of each machine instruction, a determined code (a MI which represents the end of MP) can be used, or a bit might be taken along the CM. The CM area designated for this organization purpose is shown in fig.2. Depending on certain parameters such as the mean number of MI per MP, word length, etc, one of these two extreme methods could present more befinits in CM word, with the exception of a bit in the second one, are to be sent throught the control bus to produce an MI at the processor.

An important feature of some microprogrammed machines organization is to provide a way to use certain common MP sections as subroutines. This implies the existence of a "jump" MI code. The domain of these jumps is generally restricted to a sub-set of the addressable field of the CM, for instance marking them

out within CM page limits, limiting the magnitude of the jump to a fixed maximum value, etc.

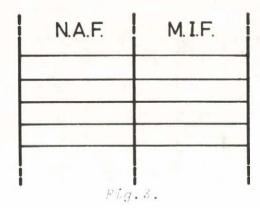

Using a unique field of the CM word for the MI executable by the processor and for the jumps (also for the end of MP when it is necessary) implies hardware complexity and speed loss which could be saved by assigning separated fields for the codes to be sent to the processor and the codes for CM address selection, as is show in fig 3.

This approach is used in the INTEL 3001/2 microprogrammable microprocessor family (5). In this series, the following must be specified in the CM word:

- in the first field: the code to be processed by the ControlMemory Unit to generate the address of the

CM word which would be read at the next

cycle

- in the second field: the code of the MI tobe executed by the central processor.

#### MULTILEVEL CONTROL MEMORY ORGANIZATION

The main idea expressed in this paper consists of the creation of - two or more levels of "addressing fields" at the CM.

This would allow the elaboration of powerful instructions (as macroinstructions) on the basis of the ones from the preceeding - level without basic software development.

More detailed comprehension of the preceeding could be reachedassuming the following:

- let us "cut" the CM into two independent blocks at the field boundary.

At the O<sup>th</sup> level are the processor's MI codes.

At the 1<sup>st</sup> level are the memory Control Unit codes, which represent addresses of the O<sup>th</sup> level MI, or some information to elaborate it, taking into account certain signals.

- by adding new memory blocks as new levels the  $2^{nd}$ ,  $3^{rd}$ , and so on, levels may be created. Always, the contents of the  $N^{th}$  level-represent the address of a  $(N-1)^{th}$  level location.

- a program at the  $N^{th}$  level is started by addressing its beginning location from the  $(N+1)^{th}$  level, and finishes when the "end of program" code is reached.

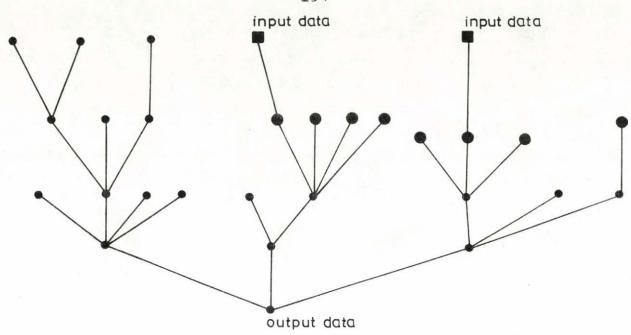

A three-level CM architecture is shown in fig 5. On the instruction bus the user's instructions, which might be from any level are present. When it is recognized (for instance) by the MCU<sub>2</sub>, the initial address of the 2<sup>nd</sup> level program which performs this instruction is generated on this unit, and the process is started. Each content of the CM<sub>2</sub> locations provokes the generation of an initial program address at CM<sub>1</sub>. Then, a program at the 1<sup>st</sup> level is started and, consequently, the corresponding one at the 0<sup>th</sup> level. The process is finished when "end of program" code is detected at the highest level.

#### ADVANTAGES OF THE MULTILEVEL CM ORGANIZATION

The benefits of such an architecture can be summarised as follows:

- the user's instruction set could be composed of higher and lower level ones, and they may ne sequenced without any rules.

- at the lowest levels high speed memory chips must be placed keeping cheaper slower memories for the highest ones. At this level the memory speed has less influence on the overall system speed. Also, this speed could be practically dependent only on the lowest level (0<sup>th</sup> and 1<sup>st</sup>) memory

- chips by employing pipe-line methods -- with only a few additional components.

- after designing a system, only a simple assembler is needed

- currently available components permit compact system implementation using multilevel control memory.

#### REFERENCES

- 1/ Wilkes, M.V.: "The best way to design an automatic calculating machine"

- Report of Manchester University Computer Inaugural Conference July 1951

- 2/ Sell, J.V.: "Microprogramming in an integrated hardware/ software system" Computer Design Jan 1975

- 3/ Casaglia, G.: "Nanoprogramming vs microprogramming" COMPUTER Jan 1976

- 4/ Baigley J.D.: "Microprogrammable virtual machines COMPUTER Feb 1976

- 5/ Intel Corporation: Intel Data Catalog 1975

Fig.1. MICROPROGRAMMED CONTROL ORGANIZATION.

Fig. 2.

The CMU area occupied by the "end of program" code is shown, for the two extreme methods: designing a code along a CM word (left) and assigning a bit along the CM (right).

The next address field (N.A.F) and the Microinstruction field could be written at the same CM word forming a microinstruction

| 1 <sup>5t</sup> LEVEL |             | M. I. C. |

|-----------------------|-------------|----------|

|                       |             | -        |

|                       |             |          |

|                       |             |          |

|                       | P . 7 . 4 . |          |

The fields had been separated and the  $1^{\rm st}$  level is formed. At the  $0^{\rm th}$  level are the microinstruction codes.

Fig. 5.

Three-level control memory organization

# СИНТЕЗ СТРУКТУР МИКРОПРОЦЕССОРОВ И МИКРОПРОЦЕССОРНЫХ СИСТЕМ

Башлаков Е.П., Кратко М.И.

Резюме

В докладе предлагается один из возможных подходов к построению формализованной теории синтеза структур микропроцессоров и микропроцессорных систем. Приводятся оценки сложности

коммутатора связи и числа микропроцессоров для проблемно-ориентированных микропроцессорных систем.

# СИНТЕЗ СТРУКТУР МИКРОПРОЦЕССОРОВ И МИКРОПРОЦЕССОРНЫХ СИСТЕМ

Башлаков Е.П., Кратко М.И.

В докладе предлагается теория формализованного синтеза структур микропроцессоров и микропроцессорных систем для различных областей применения.

Для проблемно-ориентированных микропроцессорных систем /микропроцессоров/ устанавливается верхняя оценка сложности коммутатора связей между микропроцессорами /регистрами/ и нижняя оценка числа микропроцессоров /регистров/.

Используя аппарат булевых матриц и теории графов, предлагаемая теория позволяет получить для проблемно-ориентированных микропроцессорных систем /микропроцессоров/ удобные для практического использования методы оптимизации связей в микропроцессорных системах /микропроцессорах/ и минимизации числа микропроцессоров /регистров/.

### Введение

Элементная база вычислительных машин быстро приближается к естественному пределу физических возможностей. Поэтому дальнейшее повышение производительности вычислительных машин и систем возможно за счет совершенствования их структуры и архитектуры. Современные вычислительные машины - сложные микропроцессорные системы с универсальными связями между микропроцессорами.

Большая вычислительная мощность, универсальность, гибкость, высокая живучесть, низкая стоимость вычислений, расширение контингента пользователей таких вычислительных машин оправдывают условия, направленные на развитие микропроцессорных систем.

Одной из проблем, которые здесь возникают, является формализация выбора средств и методики проектирования сложных микропроцессорных систем.

Микропроцессорную систему можно представить как совокупность микропроцессоров и средств связи, позволяющих объединить этот набор микропроцессоров в единую вычислительную систему.

Современный микропроцессор-процессор, выполненный на одном кристалле.

С точки зрения надежности каждый кристалл должен иметь небольшое количество выводов. Поэтому основные трудности в создании сложных микропроцессорных систем смещающихся в область обеспечения эффективной связи между микропроцессорами.

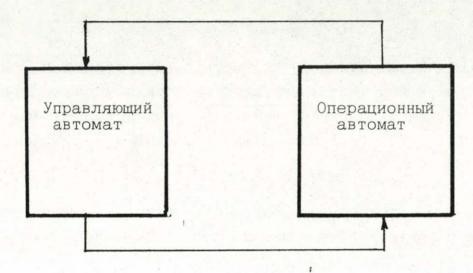

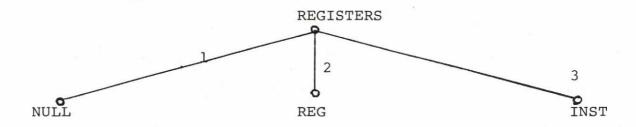

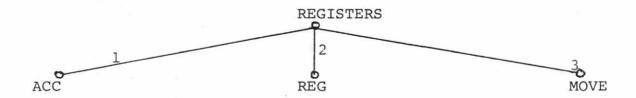

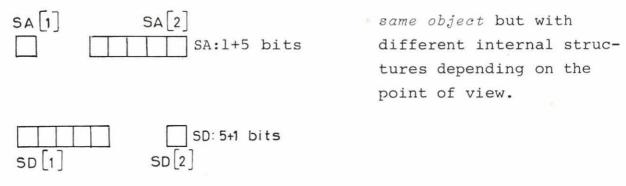

Процесс переработки информации в микропроцессорной системе /микропроцессоре/ можно представить как композицию двух

автоматов управляющего и операционного, в которой выходные

сигналы управляемого автомата совпадают с входными сигналами

операционного автомата, а его входными сигналами являются выходные сигналы операционного автомата /рис. 1/.

Рис. 1.

Конкретные области применения предъявляют различные требования к быстродействию, гибкости, надежности, живучести, и другим характеристикам системы. Поэтому актуален вопрос о максимальной эффективности использования в системе.

Для математической формулировки задач коммутации между микропроцессорами и максимальной эффективностью использования микропроцессоров в системе введем ряд понятий и определений.

# § 1. <u>Основные понятия и определения</u>

Определение 1.1.

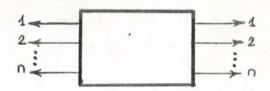

Коммутатором, точнее п -коммутатором, называется устройство K, имеющее входных и п выходных каналов, занумерованных числами от 1 до n, такое, что для каждого взаимно однозначного отображения  $\phi = \begin{pmatrix} 1,2,\ldots,n\\i_1,i_2,\ldots i \\ 1,2,\ldots i \end{pmatrix}$  множества  $\{1,2,\ldots,n\}$  на себя существует состояние  $q_{\phi}$  пребывания в котором коммутатор K имеет соединенными первой входной канал с  $i_1$  — M выходным каналом, второй входной канал с  $i_2$  — M выходным каналом и т.д. /говорят, что в состоянии  $q_{\phi}$  коммутатор реализует отображение  $\phi$  /.

Рис. 2.

### Определение 1.2.

Коммутаторная сеть определяется следующим образом.

- 1. Каждый отдельно взятый коммутатор есть коммутаторная сеть. Все входные каналы этого коммутатора являются входными каналами данной сети, все выходные каналы коммутатора ее выходными каналами.

- 3. Пусть yampa и yampa коммутаторные сети, x некоторый входной канал сети y и z некоторый выходной канал сети z . Результат присоединения канала x к каналу z также является коммутаторной сетью. Ее входными каналами являются все входные каналы сети y , за исключением канала x , и все входные каналы сети y , выходными все выходные каналы сети y и все выходные каналы сети y за исключением канала z .

- 4. Не существует никаких других коммутаторных сетей, кроме тех, которые могут быть получены конечным числом применений правил, изложенных в п. 1-3.

### Определение 1.3.

Состоянием коммунальной сети назовем совокупность состояний всех составляющих ее коммутаторов.

Пусть в коммутаторной сети выходной канал  $\mathbf{Z}_1$  коммутатора  $\mathbf{K}_1$  присоединен ко входному каналу  $\mathbf{x}_2$  коммутатора  $\mathbf{K}_2$ . Пусть коммутатор  $\mathbf{K}_1$  в состоянии  $\mathbf{q}_1$  имеет соединенным входной канал  $\mathbf{x}_4$  с выходным каналом  $\mathbf{Z}_1$ . Пусть коммутатор  $\mathbf{K}_2$  в состоянии  $\mathbf{q}_2$  имеет соединенным входной канал  $\mathbf{x}_2$  с выходным каналом  $\mathbf{Z}_2$ . Тогда, если в сети  $\mathbf{q}_1$  коммутатор  $\mathbf{K}_1$  находится в состоянии  $\mathbf{q}_1$ , а  $\mathbf{K}_2$  -  $\mathbf{b}$   $\mathbf{q}_2$ , канал  $\mathbf{X}_4$  считывается соединенным с каналом  $\mathbf{Z}_2$ . Далее отношение соединенности распространяется по транзитивности: Если  $\mathbf{q}_1$  соединен с  $\mathbf{q}_1$  и  $\mathbf{q}_2$  соединен с  $\mathbf{q}_3$  и  $\mathbf{q}_4$  соединен с  $\mathbf{q}_4$  хакие входные каналы сети соединены с какими выходными каналами, когда сеть пребывает в данном состоянии.

### Определение 1.4.

Сетью связи s микропроцессорной системы называется коммутаторная сеть с занумерованными коммутаторами /числами от 1 до n / такая, что:

- 1. В точности один входной канал каждого коммутатора является входным каналом сети. Будем нумеровать эти входные каналы теми же числами, что и соответстующие им коммутаторы.

- 2. В точности один выходной канал каждого коммутатора является выходным каналом сети. Будем также нумеровать эти выходные каналы теми же числами, что и соответствующие им коммутаторы.

- 3. Для каждого взаимно однозначного отображения  $\phi = \begin{pmatrix} 1,2,\ldots,N \\ i_1,i_2,\ldots,i_N \end{pmatrix}$  множества  $\{1,2,\ldots,N\}$  на себя существует состояние сети

${f q}_{\phi}$  , пребывая в котором сеть  ${f S}$  имеет соединенным свой первый входной канал с  ${f i}_1$ -M выходным каналом, второй входной канал - с  ${f i}_2$ -M выходным каналом, и т.д. Говорят, что в состоянии  ${f q}_{\psi}$  сеть  ${f S}$  реализует отображение  ${f \Psi}$  .

Пусть  $\mathbf{P_{i}}$  — микропроцессор с одним входом и одним вы-

Определение 1.5.

Микропроцессорной системой B , построенной на основе микропроцессора  $P_i$  и коммутаторной сети микропроцессорной системы S , является результат присоединения к каждому коммутатору сети S одного микропроцессора, причем это присоединение выполнено так, что выходной канал коммутатора, который является выходным каналом сети S , присоединяется к входу микропроцессора, а входной канал, являющийся входным каналом сети S , — к выходу микропроцессора  $P_i$  ( $i=\overline{1,N}$ ).

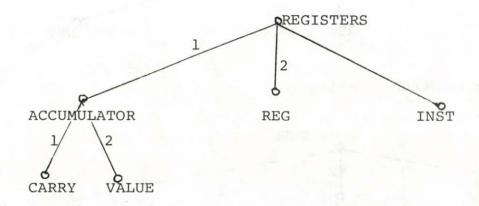

Представим процесс переработки информации в микропроцессорной системе в виде композиции из двух автоматов - управляющего A и операционного B[1-3] .

$\Phi$ ункционирование схемы из двух автоматов определяется  $\Phi$ ункциями переходов и выходов управляющего автомата A .

Определение 1.6.

Управляющим автоматом A назовем конечный абстрактный автомат Мура A =  $\langle \mathbf{x}, \mathbf{y}_A, \mathbf{Q}, \mathbf{a}_o, \mathbf{a}^*, \delta_A, \mu_A \rangle$   $\mathbf{x}$  — входной, а  $\mathbf{y}_A$  — выходной алфавиты,  $\mathbf{Q}$  — множество состояний,  $\mathbf{a}_o$  и  $\mathbf{a}^*$  — начальное и заключительные состояния,  $\delta_A$  /функция переходов/ — отображение  $\mathbf{Q} \times \mathbf{x} \times \mathbf{y}_A$  ,  $\mu_A$  /функция выходов/ — отображение  $\mathbf{Q} \times \mathbf{y}_A$  .

Определение 1.7.

Последовательность  $P^* = (a_0 = a_1, a_1, \dots a_1 = a^*)$ назовем путем в автомате A .

Та или иная последовательность выходных сигналов, выдаваемая управляющим автоматом, вызывает последовательное изменение состояний микропроцессорной системы.

Определение 1.8.

Состоянием микропроцессорной системы назовем различные наборы состояний составляющих ее элементов.

Управляющий автомат A получает от микропроцессорной системы B выходные сигналы  $\mathbf{x} (\mathbf{x} \in \mathbf{X})$ , которые представляют собою кортежи  $<\mathbf{c_1},\mathbf{c_2},\ldots,\mathbf{c_n}>$  значений логических условий, определенных соответствующим образом на микропроцессорной системе, характеризующих результаты проводимых вычислений в процессе переработки информации. Входные сигналы микропроцессорной системы отождествляются с некоторыми отображениями /преобразованиями/ множества состояний этой системы в себе. Проверяя на каждом такте работы требуемые логические условия, микропроцессорная система выдает соответствующий выходной сигнал, зависящий лишь от состояния микропроцессорной системы, но не от сигнала на входе.

Таким образом, микропроцессорная система является автоматом Мура с бесконечным числом состояний, в которой может быть обеспечен одновременный обмен информацией между всеми микропроцессорами, ведущийся каждый по отдельному тракту связи с целью избежать конфликтных ситуаций, связанных со смешиванием информации.

### Возникают задачи:

- 1./ Какое минимальное количество входов и выходов должны иметь коммутаторы, чтобы из них можно было построить сеть микропроцессорной системы, состоящую из м микропроцессоров и как эту сеть строить;

- 2./ Какое минимальное количество микропроцессоров должна иметь микропроцессорная система для решения задач в конкретных областях применения.

### § 2. Постановка задачи

Приведем математическую формулировку задачи коммутации связей в микропроцессорной системе на языке теории графов.

Определение 2.1.

Граф G , имеющий N вершин /занумерованных числами от 1 до N /, назовем информационным, если для каждой N — перестановки  $\Psi=(i_1,i_2,\ldots,i_N)$  в нем можно выделить N путей таких, что первый путь начинается в вершине номер 1 и оканчивается в вершине номера  $i_1$  , второй — начинается в вершине номера 2 и оканчивается в вершине номера 2 и оканчивается в вершине номера 2 и оканчивается в вершине номера 30 и т.д., причем никакие два различных пути не имеют ни одного общего ребра.

Определение 2.2.

Степенью графа G назовем максимальную степень его вершины /число ребер, сходящихся в этой вершине/.

Задача 1. Требуется построить N - вершинный информационный граф минимальной степени.

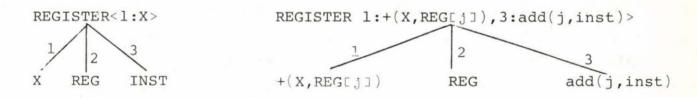

Для формальной постановки задачи II зададим процесс переработки информации в микропроцессоре  $\mathbf{p_i}$  в виде схемы из

двух автоматов  $\mathscr{A}_{i}$  и  $B_{i}$  ( $i=\overline{1,N}$ )

Каждая такая "схема" определяет некоторое, вообще говоря, частичное преобразование i на операционном автомате i - многорегистровый автомат с периодически-определенными преобразованиями i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i - i -

Пусть  $\beta = \{P_1, P_2, \dots, P_N\}$  — множество микропроцессоров в микропроцессорной системе  $\beta$ , а  $\mathcal{F}_B = \{i_{A1}, i_{A2}, \dots, i_{AN}\}$  — множество преобразований, осуществляемых на множестве  $\beta$  выходными сигналами управляющего автомата A.

Сложность микропроцессора ho (P $_{f i}$ ) определим формулой:

$$p(P_i) = p(f_{Ai}) + p(B_i) + p(\phi_i)$$

/2.1/, где

ho (  $_{

m Ai}$  )- сложность схемы, реализующих преобразование  $^{\dag}$   $_{

m Ai}$  ,  $_{

m CIO}$  ( $_{

m B}_{

m i}$ ) - сложность операционного автомата  $_{

m B}_{

m i}$  , а  $_{

m P}$  ( $_{

m P}_{

m i}$ )- сложность коммутатора связи  $_{

m P}_{

m i}$  микропроцессора  $_{

m P}_{

m i}$  .

Из определения /1.5/ следует, что конструктивными элементами микропроцессорной системы  ${\bf B}$  являются микропроцессоры и коммутаторная сеть  ${\bf s}$  , связывающая микропроцессоры в единую систему.

Отсюда искомая оценочная функция /функционал/ сложности автомата в может быть представлен в виде:

$$F(B) = \sum_{i=1}^{N} p(P_i)$$

/2.2/

Используя в качестве критерия оптимальности минимальное значение этого функционала, получаем, что задача синтеза и минимизации числа микропроцессоров микропроцессорной системы сводится к отыскиванию такой технической реализации автомата в при заданном функционировании схемы из двух автоматов, чтобы:

$$\min_{\substack{(P_{i\kappa})\in F(B)}} F(B) = \sum_{\kappa=1}^{m} P(\tilde{P}_{i\kappa})$$

$$M$$

/2.3/

$$\min_{\mathbf{F}^*(\mathbf{B})} = \sum_{\kappa=1}^{m} \tilde{\mathbf{P}}_{i\kappa}$$

$$\tilde{\mathbf{P}}_{i\kappa} \in \mathbf{F}^*(\mathbf{B})$$

$$(2.4)$$

Учитывая то обстоятельство, что конструктивными элементами операционного автомата  $B_i$  являются регистры и комбинационные схемы, реализующие заданные на этих регистрах преобразования, формулы /2.1 – 2.4/ для синтеза многопроцессорных автоматов будут иметь аналогичный вид при соответствующей интерпретации слагаемых.

## § 3. Построение сети связи микропроцессорной системы

С целью решения задачи 1, определим функцию  $\Phi(N)$  следующим образом:  $\Phi(N)$  равно минимуму степеней информационных графов, имеющих ровно N вершин.

Теорема 3.1. Справедлива следующая нижняя оценка:

$$S(N) \ge C_1 \frac{\log N}{\log \log N}$$

Доказательство. Пусть граф G имеет N вершин и максимальная степень его равна  $\alpha(\alpha > 1)$  . Очевидно, что в окрестности радиуса  $\frac{\log_{\alpha} N}{2}$  любой его вершины находится не более, чем  $\frac{N}{2}$  вершин. Следовательно, можно задать по крайней мере  $\frac{N}{2}$  пар номеров вершин  $\langle \mathbf{x}_i, \mathbf{y}_i \rangle$  ( $1 \le i \le \frac{N}{2}$ ) таких, что все  $\mathbf{x}_i$  - различные числа, и все  $\mathbf{y}_i$  - различные, и для каждого  $\mathbf{x}_i$  вершина номера  $\mathbf{x}_i$  в графе G находится на расстоянии не меньше, чем  $\frac{N\log_{\alpha} N}{4}$  от вершины номера  $\mathbf{y}_i$ . Чтобы в графе G можно было провести все пути, соответствующие этим парам, т.е. такие, что  $\mathbf{i}$  -ый путь начинается в вершине

номера  $_{i}$  и оканчивается в вершине номера  $_{i}$  , и никакие два различные пути не имеют ни одного общего ребра, число ребер в графе  $_{i}$  должно быть не меньше  $_{i}$   $_$

$$N_{\alpha} \ge \frac{Nlog_{\alpha} N}{4}$$

или  $\alpha \ge 1/4 \log_{\alpha} N$  . Решение уравнения  $\mathbf{x} = \log n$  , как известно, асимптотически равно  $\frac{\log n}{\log \log n}$  . Значит для того, чтобы выполнялось приведенное выше неравенство, степень графа G должна быть по порядку  $\geq \frac{\log N}{\log \log N}$  . Теорема доказана. Теперь покажем, что существуют информационные графы степени <  $\frac{\log 2^N}{\log 2^N}$ . Теорема доказа-. Воспользуемся следующим классом графов. Чтобы упростить его описание положим, что число и является степенью двойки и расположим все вершины на плоскости в точках с целочисленными координатами в виде прямоугольника шири- $\log_2 N$  . Каждый ряд содержит N вершин и и высоты таких рядов имеется  $\log_2 N$  , так что всего граф содержит вершин. Ребра проводятся только между вершинами двух соседних рядов, причем в зависимости от того, какая пара рядов соединяется, ребра проводятся по разному. Первый /сверху/ ряд соединяется со вторым так, что ребра проводятся между вершинами первого и второго ряда, имеющими одинаковые номера по модулю  $\frac{N}{2}$  . Чтобы соединить второй ряд с третьим надо разбить их оба на части -  $\{1,2,\ldots,\frac{N}{2}\}$  $M \left\{ \frac{N}{2} + 1, \frac{N}{2} + 2, \dots, N \right\}$  , M в каждой части отдельно соединить вершины, имеющие одинаковые  $\frac{N}{4}$  . Чтобы соединить ряды  $_{\mathsf{K}}$  и  $_{(\mathsf{K}+1)}$  надо номера по модулю каждую часть, на которую был разбит ряд к при соединении его с рядом  $(\kappa-1)$  , разбить пополам, так же разбить ряд  $(\kappa+1)$ и соединить отдельно в каждой из частей вершины, имеющие одинаковые номера по модулю числа в два раза меньшего, чем для рядов  $(\kappa-1)$  и  $\kappa$  .

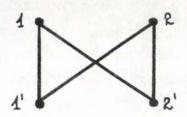

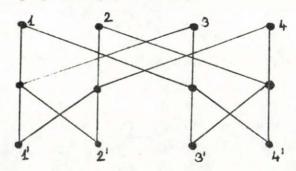

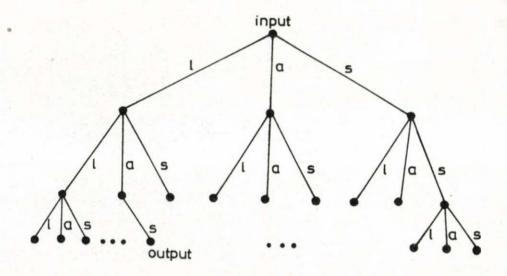

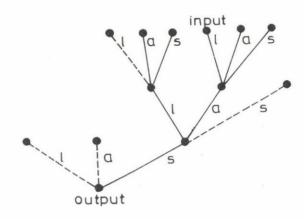

Тот же класс графов может быть задан индуктивно следующим образом. Граф ранга 1 это граф, изображаемый на рис. 3.

Рис. 3.

У него четыре вершины, две из них, называемые верхними, это вершины 1 и 2, нижние - вершины 1' и 2'. Граф ранга 2 строится из двух графов ранга 1 следующим образом.

Два графа ранга 1 рисуются рядом, и непосредственно над каждой верхней вершиной обоих графов рисуется еще по одной вершине.

Каждая верхняя вершина графа ранга соединяется ребрами с вершиной, находящейся непосредственно над ней и с вершиной, находящейся непосредственно над вершиной того же номера во втором графе ранга 1.

Полученный граф изображен на рис. 4.

Рис. 4.

Верхние вершины в нем нумеруем числами 1, 2, 3 и 4.

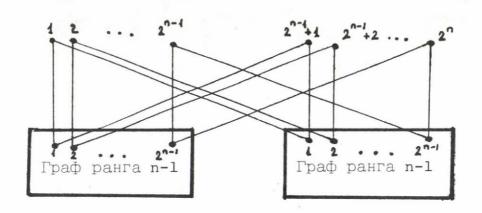

Чтобы получить граф ранга п поступают аналогично. Берут два графа ранга (n-1) . Над каждой верхней вершиной каждого из этих графов рисуют еще одну вершину. Соединяют каждую верхнюю вершину графа ранга (n-1) , с непосредственно находящейся над ней вершиной и с вершиной, непосредственно находящейся над верхней вершиной того же номера в другом графе ранга (n-1) , как показано на рис. 5.

Рис. 5.

Нумеруем верхние вершины нового ранга  $\,$   $\,$  числами от  $\,$  1 до  $\,$   $\,$   $\,$  2  $\,$   $\,$  .

Пусть  $N=2^{n}$  . Для нас будут важными следующие свойства введенных графов.

- 1. Степень каждой вершины, кроме вершин, расположенных в верхнем и в нижнем ряду, равна четырем. Степень вершин, расположенных в верхнем и нижнем ряду, равна двум.

- 2. Любая полоса высоты  $\tau$  в графе ранга n , при условии, что  $\tau$  намного меньше n /т.е. подграф на вершинах, которые находятся в рядах с номерами  $\{i,i+1,\ldots,i+\tau\}$  ( $1 \le i \le n-\tau$ ) , распадаются на  $2^{n-\tau}$  несвязных частей, являющихся графами ранга  $\tau$  /.

Если к нижнему ряду вершин графа ранга  $^{n}$  "приклеить" зеркальное отображение его, то хорошо известно, что в получен-

ном графе  $G_1$  для любой N-перестановки  $\phi = \{i_1, i_2, \dots, i_N\}$ можно выделить N путей, соединяющих вершины верхнего ряда с вершинами нижнего ряда так, что первый путь соединяет первую вершину с  $i_1$ -ой, второй - вторую вершину с  $i_2$ -ой и т.д., и никакие два разные пути не имеют ни одного общего ребра. Поэтому, если попарно склеить соответствующие вершины верхнего и нижнего рядов графа  $G_1$  , то для этого множества вершин /назовем их основными/ полученный граф  ${\tt G}_2$  является информационным. Это значит, что для любой N-перестановки  $\phi = (i_1, i_2, ..., i_N)$  в графе  $G_2$  можно выделить N путей так, что первый путь начинается в первой основной вершине и оканчивается в  $i_1$ -ой основной вершине, второй начинается во второй основной и оканчивается в  $i_2$ -ой основной вершине и т.д., и никакие два различные пути не имеют ни одного общего ребра. Разумеется эти пути проходят не только через основные, но и через вспомогательные вершины.

Чтобы превратить граф  $G_2$  просто в информационный граф с вершинами, надо разбить все его вершины на N групп так, чтобы в каждой группе была одна основная, некоторое число вспомогательных вершин, и "стянуть" такую группу в одну вершину.

Наш граф  $G_2$  имеет  $2N\log_2N$  вершин, следовательно, каждая группа содержит  $2\log_2N$  вершин, и если при разбиении вершин на группы не заботиться, какие вспомогательные вершины попадают в одну группу, то полученный информационный граф будет иметь степень  $8\log_2N$ . Если же стараться выделить группы так, чтобы каждая группа вершин была графом ранга  $\log_2n$ , то степень "стянутой" вершины может быть уменьшена до  $\log_2 N$ . Действительно, разделим граф  $G_2$  на полосы высотой  $(\log_2n-\log_2\log_2n)$  . Каждая полоса, согласно отмеченному выше свойству 2/, распадается на  $\log_2 N$  частей ширины  $\log_2 N$  . Каждая часть соединяется с остальной частью графа только ребрами, исходящими из верхнего и нижнего рядов. Поэтому, если стянуть такой подграф в одну вершину,

то ее степень будет равна /см. свойство 1/  $4\frac{\log_2 N}{\log_2 \log_2 N}$  . Всех частей, на которые распадается граф  $G_2$  , имеется

$$2 \frac{N \log_2 \log_2 N}{\log_2 N} \left( \frac{\log_2 N}{\log_2 \log_2 N - \log_2 \log_2 \log_2 N} \right) < 4N \qquad ,$$

т.е., если стянуть все такие части к N основным вершинам, то получим /при больших N / информационный граф, имеющий степень по порядку равную  $c_2 \frac{\log N}{\log \log N}$  , где N - число его вершин. Таким образом, описанная нами конструкция информационных графов позволяет сформулировать следующую теорему.

<u>Теорема 3.2</u>. С точностью до порядка /мультипликативной константы  $\mathbf{c}$  /

$$\Phi(N) = C \frac{\log N}{\log \log N}$$

# § 4. Синтез структур микропроцессорных систем

С целью решения задачи II, рассмотрим схему из автоматов и  ${\bf B}$  . Функционирование "схемы" - процесс выполнения некоторого алгоритма, а преобразование  ${\bf I}_{\bf A}$  - функция, вычисляемая этим алгоритмом на множестве  ${\bf B}$  .

Через  $^{i}$   $^{i}$

Через  $^{\mathfrak{f}(\mathbf{j})}_{\mu_{\mathbf{A}}(\mathbf{a})}$  обозначим функцию, вычисляемую на множестве микропроцессором  $^{\mathbf{P}}_{\mathbf{j}}$ , и представим ее в виде кортежа:

$$\langle P_1, P_2, ..., P_N, f^{(j)} \mu_A(a), P_j \rangle$$

/4.1/

Полагаем, что для выполнения преобразования  $i^{(j)}\mu_A(a)$  информация с микропроцессоров  $(P_1,P_2,\dots,P_N)$  последовательно пересылается на микропроцессор  $P_j$ , а память микропроцессоров неограничена.

Значение функций  $^{\mathfrak{f}(\mathbf{j})}_{\mu_{\mathbf{A}}(\mathbf{a})}$  на множесте  $^{\mathfrak{g}}$  существенно зависит не от всех аргументов  $^{\mathfrak{f}(\mathbf{j})}_{\mu_{\mathbf{A}}(\mathbf{a})}$  представим в виде:

$$\langle P_1, P_2, ..., P_N, f^{(j)} \mu_A(a), P_j \rangle$$

/4.2/, где

$$\tilde{P}_i$$

=

$$\begin{cases} P_i, & \text{если значение функции} & \tilde{\mathfrak{f}}^{(j)}_{\mu_A}(a) \\ & \text{существенно зависит от } P_i, \\ & 0 - \text{в противном случае.} \end{cases}$$

Каждому преобразованию  $\mathfrak{f}_{\mu_{\mathbf{A}}(\mathbf{a})}$  автомата  $\mathfrak{B}$  будет соответствовать кортеж вида /4.2/. Это преобразование вызывается в автомате  $\mathfrak{B}$  выходным сигналом  $\mu_{\mathbf{A}}(\mathbf{a})$  автомата  $\mathfrak{A}$ . Поставим в соответствие каждому выходному сигналу  $\mu_{\mathbf{A}}(\mathbf{a})$  кортеж вида:

$$<\mu_{A}^{(1)},\mu_{A}^{(2)},\dots,\mu_{A}^{(n)},$$

f  $\mu_{A}(a)$ , j> , где

$$\mu_{A}^{(i)}=\left\{ \begin{array}{ll} 1,\; \text{если} & P_{i}\neq 0 \quad \text{в выражении /4.3/,} \\ 0-\text{в противоположном случае,} \end{array} \right.$$

j - номер микропроцессора  $\ P_j$  , на котором осуществляется преобразование  $\ j \ \mu_A(a)$  .

Обозначим множество кортежей вида /4.3/ автомата  ${\bf A}$  через  ${\bf \beta}_{\mu}$  .

Определение 4.1.

ABTOMAT  $\mathcal{A}_{B} = \langle \mathbf{x}, \beta_{\mu}, \mathbf{Q}, \mathbf{a}_{o}, \mathbf{a}^{*} \delta_{A}, \mu_{AB} \rangle$  назовем  $_{B}$  - автоматом.

$^{\it M}_{\it B}$  - автомат содержит информацию о тех и только тех микропроцессорах автомата  $^{\it B}$  , которые необходимы только и только для выполнения преобразования  $^{\it I}\,\mu_{\it A}(a)$  в состоянии  $^{\it a}$  . В этом же состоянии некоторые микропроцессоры могут хранить информацию для выполнения преобразований в следующих за состоянием  $^{\it A}$  состояниях. С целью выявления таких микропроцессоров введем определение.

Определение 4.2.

Путем  $P_j$  занятости микропроцессора  $P_j$  в  $\mathcal{A}_B$  -автомате назовем такой максимальный путь  $P_j$ =( $a_{\kappa 1}, a_{\kappa 2}, \ldots, a_{\kappa t}$ ), который является отрезком некоторого пути  $P^*$ , и такой, что:

$\mu_{A_B}^{(n+i)}(a_{\kappa 1})$  = j, a  $\mu_{A_B}^{(j)}(a_{\kappa 1})$  = 1, и для каждого  $a_{\kappa i}^{(1\leq i\leq t)}$   $\mu_{A_B}^{(n+2)}(a_{\kappa i})$   $\mu_{A_B}^{(n+2)}(a_{\kappa i})$   $\mu_{A_B}^{(n+2)}(a_{\kappa i})$  назовем начальным состоянием пути  $\mu_{A_B}^{(n+2)}(a_{\kappa i})$  , а состояние  $\mu_{A_B}^{(n+2)}(a_{\kappa i})$  , а состояние  $\mu_{A_B}^{(n+2)}(a_{\kappa i})$  назовем  $\mu_{A_B}^{(n+2)}(a_{\kappa i})$

Иными словами, путь  $p_{\bf j}$  занятости микропроцессора  $p_{\bf j}$  - максимальный путь, на котором состояниями микропроцессора являются только значения результата преобразования  ${}^{i}$   $\mu_{A_B}(a_{\kappa_1})$  , осуществляемого в начальном состоянии  $a_{\kappa_1}$  , а которое обязательно должно быть аргументами преобразования в конечном состоянии  $a_{\kappa_+}$  пути  $p_{\bf j}$  .

Используя автомат  $\mathscr{A}_B$  и определение /4.2/ с помощью методов теории графов можно построить новый  $\mathscr{A}_C$  - автомат:  $\mathscr{A}_C = < \mathfrak{X}, \beta_C, \ _1, a_o, a^*, \delta_A, \mu_{A_C} > \qquad , \ _B \ _{KOTOPOM} \ _{YOPOM} \ _{YOPOM}$

$$<\mu_{A_c}^{(1)}, \mu_{A_c}^{(2)}, \dots, \mu_{A_c}^{(n)}, \mu_{A_c}^{(n)}, j>$$

/4.4/

где

$$\mu_{\mathbf{A_c}}^{(\mathbf{i})} = \left\{ egin{array}{lll} 1, & \text{если микропроцессор} & \mathbf{P_i} & \text{содержит информа-} \\ & & \text{цию для выполнения преобразования} & \mathbf{\mu_{A(a)}} \\ & & \text{или преобразований, выполненных в следую-} \\ & & \text{щих за состоянием} & \mathbf{a} & \text{состояниях} & \mathbf{a} & \mathbf{;} \\ & & 0 - \mathbf{B} & \text{противном случае}. \end{array} \right.$$

Пусть задан  ${}^{\mathscr{A}}_{\mathbf{C}}$  — автомат микропроцессорной системы  $\mathbf{B}$  . Через  $\mathbf{T_i}$  — обозначим подмножество состояний автомата  $\mathbf{A}$  , на котором используется микропроцессор  $\mathbf{P_i}$  — в микропроцессорной системе  $\mathbf{B}$  .

Определение 4.3.

Графом  $Q=(\beta,\Gamma)$  микропроцессорной системы B назовем конечный неориентированный граф с множеством вершин  $\beta = \{\,P_1,P_2,\ldots,P_N^{}\}\,$  , в котором вершины  $P_j$  и  $P_i$  смежны тогда и только тогда, когда выполняется условие  $T_j \cap T_i \neq \emptyset$  .

Определение 4.4.

Отмеченным графом  $Q_B = (\beta, \mathscr{F}_y, F)$  микропроцессорной системы B назовем такой граф  $Q = (\beta, \Gamma)$  , в котором каждой вершине  $P_i$  приписано множество функций, вычисляемых микропроцессором  $P_i$  .

Определение 4.5.

Определение 4.6.

Последовательность элементарных гомоморфизмов  $\phi = (\epsilon_1 \ \epsilon_2 \dots \ \epsilon_{\kappa}) \qquad \text{графа} \ Q \ /\text{графа} \ Q_B \ / \ \text{назовем гомоморфизмом}$   $\phi \qquad \text{графа} \ Q \ /\text{графа} \ Q_B \ /.$

Определение 4.7.

Гомоморфизм ф графа Q /графа  $Q_B$  / назовем полным порядка n , если его образ  $\phi$  (Q) (  $(Q_B)$ ) является полным графом на n вершинах.

Наименьший порядок всех полных гомоморфизмов графа Q/графа  $Q_B$  / обозначим  $\lambda(Q)(\lambda(Q_B))$  . В теории графа известна следующая теорема.

Теорема 4.8. Для любого графа  ${\bf Q}$  и его элементарного гомоморфизма  $\epsilon$

$$\lambda(Q) \leq \lambda(\epsilon Q) \leq 1 + \lambda(Q)$$

.

Следствие. Для любого гомоморфизма ф графа Q

$$\lambda$$

(Q)  $\leq \lambda$  (Q).

Пусть задан граф Q . Рассмотрим полный гомоморфизм графа Q на граф Q' с порядком  $\lambda(Q)$  . Отображение определяется разбиением множества вершин  $\beta$  графа Q на  $\lambda(Q)$  непересекающихся подмножествах  $B_{\kappa}(\kappa=\overline{1,X(Q)})$  попарно несмежных вершин, т.е.

$$\beta = \bigcup_{\kappa=1}^{\lambda(Q)} B_{\kappa} ; B_{i} \cap B_{j} = \phi(i\neq j)$$

/4.5/

Условие /4.5/ в силу определения /4.3/ равносильно выполнению условия:

$$T_B = \bigcup_{\kappa=1}^{\lambda(Q)} T_{\kappa}$$

;  $T_i \quad T_j = \phi (i \neq j)$ .

Поэтому каждой вершине графа Q может быть сопоставлен микропроцессор в новом автомате B, . Обозначим через —число микропроцессоров в автомате B, .

Таким образом, описанная нами конструкция позволяет сформулировать следующую теорему .

Теорема 4.9. Для микропроцессорной системы  $^{\mathbf{B}}$  , реализующей функцию  $_{\mathbf{A}}$  , справедлива следующая нижняя оценка:

### 7 > \(\lambda(\text{Q})

Граница  $\tau$  = $\lambda(Q)$  достигается при минимизации графа Q . Как правило, микропроцессорная система задается графом  $Q_B$  .

Таким образом, теорема 4.9. сводит проблему синтеза микропроцессорной системы  ${\bf B}$  к оптимизации графа  ${\bf Q}_{\bf B}$  , а проблему минимизации числа микропроцессоров в микропроцессорной системе к минимизации числа вершин графа  ${\bf Q}$  .

Методы оптимизации таких графов известны.

### Заключение

Описанный выше подход к построению формальной теории сложных микропроцессорных систем по сути свел эту важнейшую и сложнейшую проблему современной вычислительной техники к решению следующих задач.

- 1. Выбору минимального числа микропроцессоров микропроцессорной системы.

- 2. Построению сети связи микропроцессорной системы с выбранным числом микропроцессоров.

- 3. Синтезу и минимизации управляющего автомата известными методами [4].

Используя аппарат булевых матриц и теории графов, описанный подход позволяет создать системы с перестраиваемой структурой связей, что упрощает переход от одного варианта системы к другой путем их перепрограммирования с помощью современных ЭВМ для проблемно-ориентированных микропроцессорных систем.

В заключение авторы отмечают, что настоящая работа выполнена как развитие идей академика В.М. Глушкова о создании вычислительных систем будущего.

### ЛИТЕРАТУРА

- В.М. Глушков: О применении абстрактной теории автоматов для минимизации микропрограмм, "Известия АН СССР". "Техническая кибернетика", № 1, М., 1964.

- В.М. Глушков: Теория автоматов и вопросы проектирования структур цифровых машин, журн. "Кибернетика", № 1, К., 1965.

- 3. В.М. Глушков: Теория автоматов и формальные преобразования микропрограмм, журн. "Кибернетика", № 5, К., 1965.

- 4. В.М. Глушков: Синтез цифровых автоматов, Физматгиз, М., 1962.

# СТЫКОВКА ЭВМ В МНОГОМАШИННЫХ СИСТЕМАХ НА БАЗЕ МИКРО-ЭВМ

### В. Хенцлер

НП Роботрон НИЦ, г. Дрезден, ГДР

Появление больших интегральных схем сегодня создает возможность разработки многомашинных систем с экономически допускаемыми затратами и применения их в широких масштабах в народном хозяйстве. При этом затраты на стыковку и ее производительность сильно зависят от выбираемой стратегии совместного включения. Одновременно вид стыковки решающим образом влияет на поведение и надежность всей многомашинной системы.

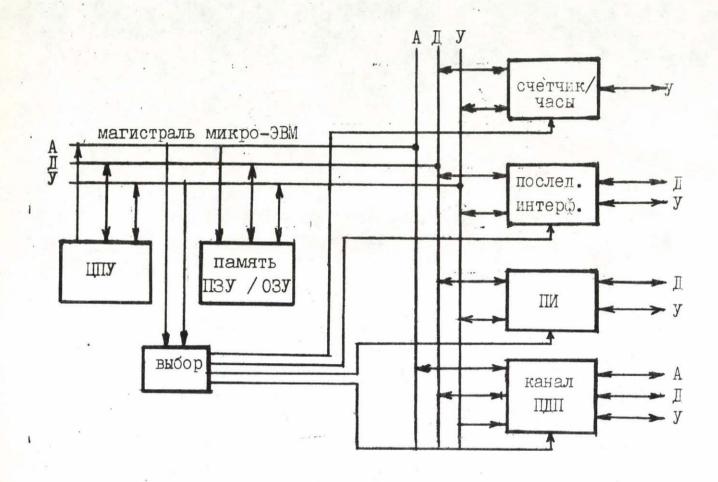

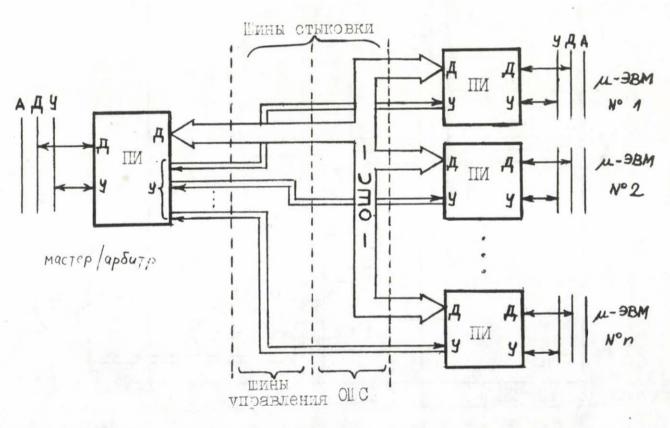

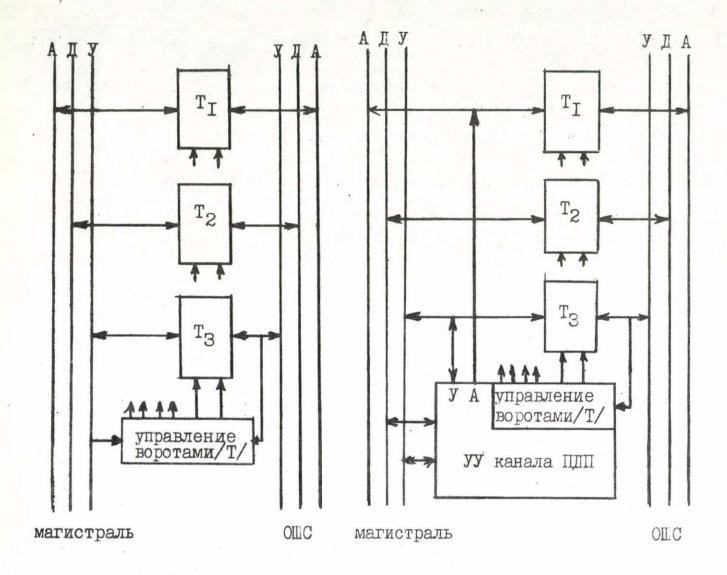

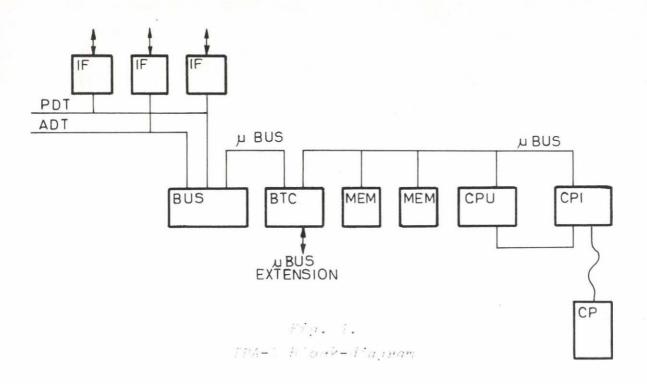

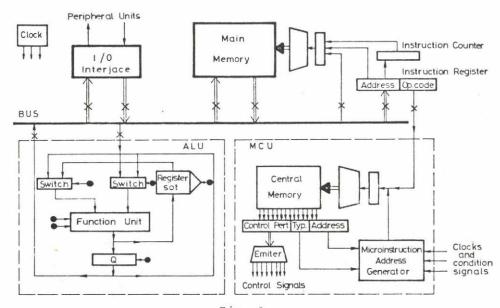

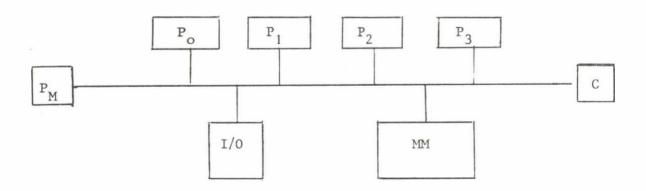

Основные функциональные единицы микро-ЭВМ, смотря со стороны стыковки, изображены на рис. 1. Ядро микро-ЭВМ состоит из центрального процессорного устройства /ЦПУ/ и из собственной памяти /ПЗУ и ОЗУ/. Коммуникация с внешней средой происходит с помощью приведенных четырех типов устройств /БИС-ов/ для ввода/вывода. Коммуникация ЦПУ с устройствами ввода/вывода и памятью, т.е. внутри микро-ЭВМ, производится через системную магистраль, которая состоит из адресной шины, шины данных и шины управления.

Приведенные на рис. 1 устройства ввода/вывода дальше рассматриваются подробнее относительно их применяемости для стыковок в многомашинных системах.

Рис. 1. Блок-схема микро-ЭВМ

# 1. Устройство счетчика/часов

Самое простое устройство — это устройство счетчика/часов, которое может выдавать к ЦПУ импульсы /прерывания/ в определенных интервалах времени и считывать определенные внешние события /импульсы/. Длительность временного интервала между импульсами и начальное состояние счетчика можно программно задавать и также можно опрашивать текущее состояние счетчика.

Устройство счетчика/часов непосредственно не применимо для стыковки с микро-ЭВМ, так как через него не проходит ника-кого прямого обмена данными. Несмотря на это, его применяют в многомашинных системах для обеспечения времен реакций и обслуживания.

## 2. Последовательный интерфейс

Этот интерфейс является традиционным интерфейсом для стыковки ЭВМ между собой, так, например, в вычислительных сетях

для телепередачи данных. В области микро-ЭВМ последовательный

интерфейс получает особенное значение для подключения медленных

внешних устройств.

Для стыковки незначительное количество соединительных проводов последовательного интерфейса особенно выгодно, если между ЭВМ имеются относительно большие расстояния. Это, например, имеет место в децентрализированных многомашинных системах на базе микро-ЭВМ для контроля и управления производственными процессами. Из-за малых затрат на соединения /кабеля/ здесь имеется возможность, существенно повысить надежность линии передачи посредством многократного резервирования, причем вся вычислительная система остается еще экономически выгодной.

За счет передачи незначительного количества информаций во времени первые два вида стыковки годятся только условно для сопряжения ЭВМ в многомашинных системах с большим потоком информаций. Этому требованию в большей степени удовлетворяют следующие два вида стыковки.

# 3. Параллельный интерфейс

Для параллельного интерфейса характерно, что шина данных подключается полностью параллельно к Общей шине стыковки /ОШС/, а не поразрядно, как при последовательных интерфейсах. Это ведет к значительному увеличению скорости обмена данными, но и сопровождается повышенными затратами на аппаратные средства. Такая стыковка называется и периферийной стыковкой, что обусловливается тем, что устройства ввода/вывода параллельного интерфейса /ПИ/ со стороны микро-ЭВМ обслуживаются как внешние устройства, т.е. ЦПУ должно обращаться к ним с операцией ввода/вывода по определенным адресам. Устройство параллельного интерфейса, при этом, находится в определенном состоянии /го-

тов или занят/; если оно готово, - оно должно быть в состоянии временно запоминать полученные от ЦПУ данные и потом самостоятельно обмениваться с устройством ПИ принимающей ЭВМ сигналы готовности передачи/приема и, наконец, передать данные. Мощность такой периферийной параллельной стыковки в значительной мере зависит от следующих факторов:

- 1. С какой скоростью микро-ЭВМ может выдавать данные устройству ПИ /т.е. какие временные затраты потребуются, чтобы пересчитать счетчики адреса и длины массива данных и чтобы организовать некоторое условие окончания обмена/.

- 2. Содержатся ли в устройстве ПИ специальные аппаратные средства для управления самостоятельным обменом данными.

- 3. Сообщает ли устройство ПИ ЦПУ об окончании передачи или ЦПУ приходится анализировать признак окончания передачи программным путем. То же касается и сигнала окончания приема данных.

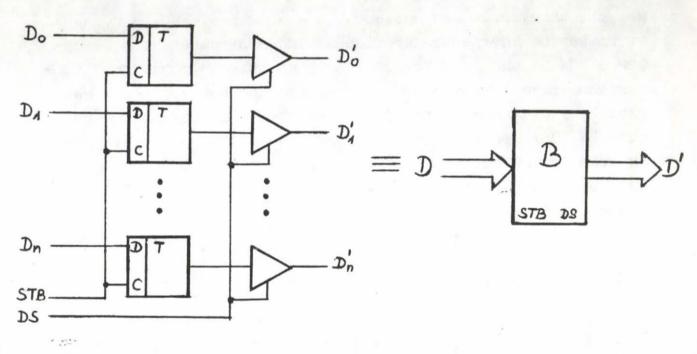

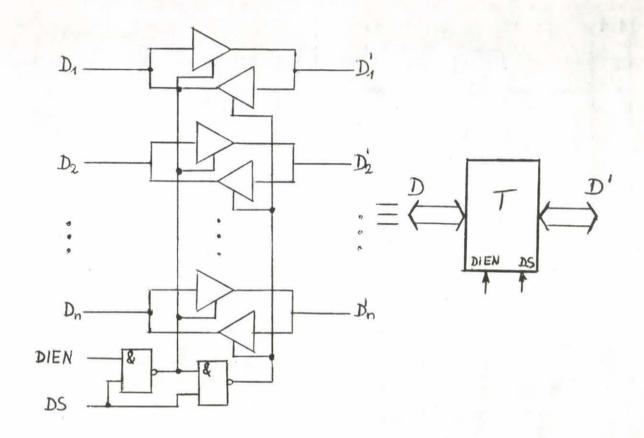

Основной элемент ПИ представляет собой регистр, выходы которого подключаются через усилитель с третьим высокоомным состоянием к шине стыковки. В зависимости от вида управления обменом данными к этой схеме надо еще добавить логику для управления обменом данными и логику прерывания. Современная схемотехника выдвигала для этого уже удобные БИС-ы для ввода/вывода с внешними устройствами, но они до сих пор еще не пригодны для нужд стыковки микро-ЭВМ между собой.

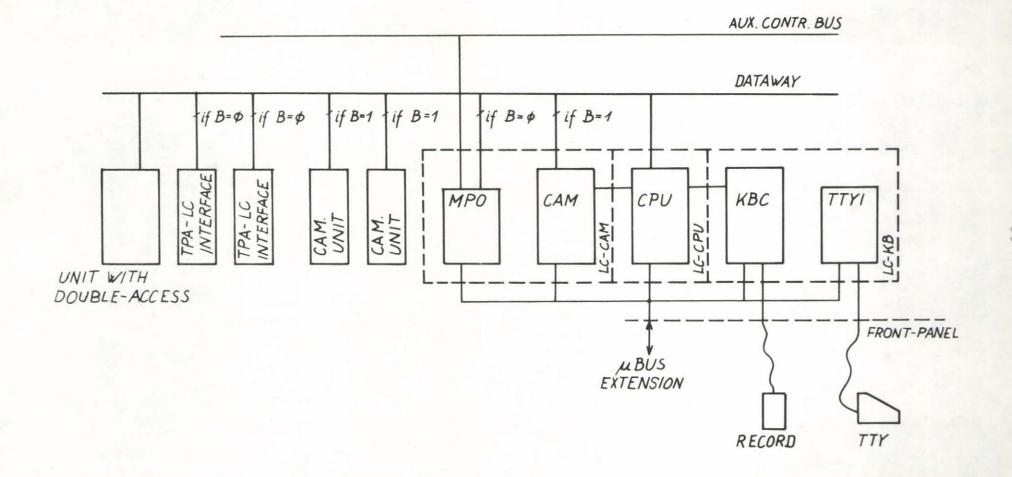

Основное звено ПИ представлено на рис. 2. Блок-схема многомашинной системы со стыковкой через БИС-ы устройства ПИ изображена на рис. 3. Здесь устройства ввода/вывода /ПИ/ всех ЭВМ соединяются через двухнаправленную Общую шину стыковки /ОШС/ и шину управления стыковкой. При этом ОШС, кроме шины данных, содержит и линии управления обменом данными. Управление и распределение ОШС принадлежит одной ЭВМ, которая станет, таким образом, управляющей. В зависимости от места этой ЭВМ в многомашинной системе, т.е. от места в информационном пото-

Рис. 2. Регистр/усилитель с высокоомным выходом /В/.

Рис. 3. Блок-схема стыковки микро-ЭВМ через устройства ПИ.

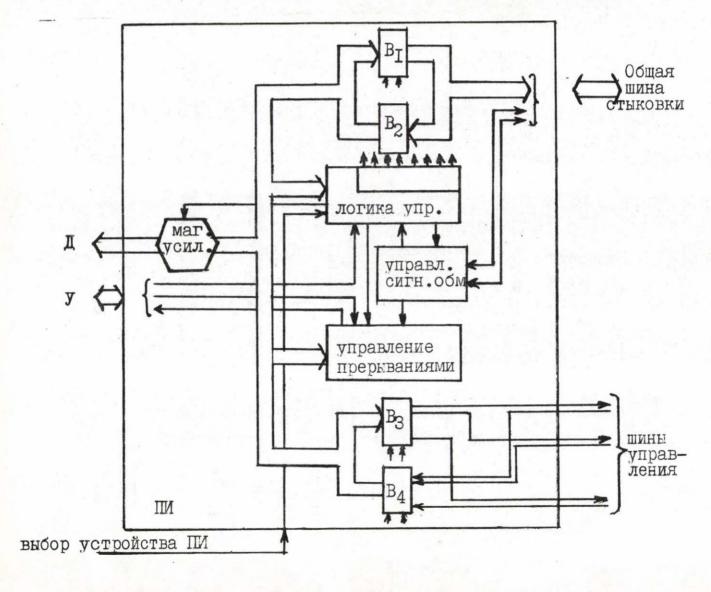

ке, она называется или мастером, или арбитром. Рис. 4 показывает примерное внутренное построение БИС-а параллельного интерфейса /ПИ из рис. 3/. Устройство ПИ содержит 4 регистра, включая усилители с третьим высокоомным состоянием соответственно рис. 2, управляемые логикой управления ПИ. Два из этих регистров  $B_1$ ,  $B_2$ / предназначены для двухнаправленного обмена данными между шиной данных микро-ЭВМ и шиной данных ОШС. Остальные два регистра служат для приема  $B_4$ / и выдачи  $B_3$ / сигналов запроса и ответа для эксплуатации ОШС. Логика управления ПИ собдержит, кроме устройства управления, регистры состояния и режи-

Рис. 4. Блок-схема устройства /БИС-а/ параллельного интерфейса ПИ.

мов работ. Выдача и ввод данных осуществляется с помощью сигналов "готов" и "строб" линии управления ОШС посредством логики управления обменом данными. Логика прерывания обеспечит генерирование требуемых сообщений об окончании выаода или запросов ввода для ЦПУ через шину управления системой магистрали микро-ЭВМ.

В более простом варианте параллельного интерфейса /только применяя аппаратные средства из рис. 2 без логики управления/ выше приведенные сигналы управления должны быть анализированы и генерированы программным путем, в результате чего значительно уменьшается скорость обмена данными.

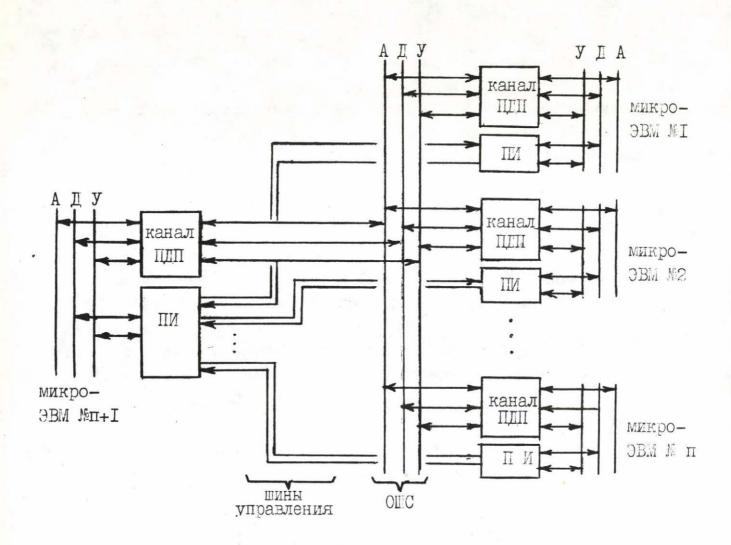

### 4. Прямой доступ к памяти

Все пока описанные варианты стыковки не достигали теоретически возможную скорость обмена данными, максимальная величина которой определяется временем выработки данных из устройств памяти. Но выигрыш в скорости передачи при прямом доступе к памяти /ПДП/ связан с повышенными затратами на аппаратные средства. Обычно принцип прямого доступа к памяти реализуется подключением всей системой магистрали микро-ЭВМ /адресной шины, шины данных, шины управления/ к ОШС /смотри рис. 5/. Кроме схем канала ПДП, необходимы еще регистры для выдачи запроса и для получения сигнала предоставления ОШС как и при стыковке через параллельный интерфейс ПИ. В зависимости от выбираемого режима работы регистры обмена данными /В, Во/ и логика управления обменом данными схмы ПИ /рис. 4/ могут применяться или не применяться. Блок-схема канала ПДП из рис. 5 изображена на рис. 7 и 8 и для двух вариантов прямого доступа к памяти. Рис. 6 показывает основной элемент канала ПДП, представляющий собой двухнаправленный управляемый вентиль.

Рис. 5. Стыковка микро-ЭВМ через прямой доступ к памяти.

Рис. 6. Основной элемент канала ПДП.

На рис. 7 указано более простое, но и более медленное, исполнение канала ПДП, при котором системная магистраль одной ЭВМ полностью подключается к системной магистрали другой ЭВМ. Для этого необходимо обеспечить, чтобы до подключения ЦПУ к одной микро-ЭВМ оно отключалось бы от своей системной магистрали и перешло бы в пассивное состояние. Другое ЦПУ получит тогда управление обоих системных магистралей и программно управляет обмен данными между обемими системами. Так как в данном случае стыковки требуется еще больший объем организационных затрат максимальная скорость обмена данными не достигается. Скорость более близкая к максимальной достигается с применением дополнительной схемы - т.е. специальное устройство управления /УУ/ канала ПДП /см. рис. 8/.

Рис. 7. Канал ПДП, управляемый Рис. 8. Канал ПДП, управляемый программно от ЦПУ. от УУ канала ПДП.

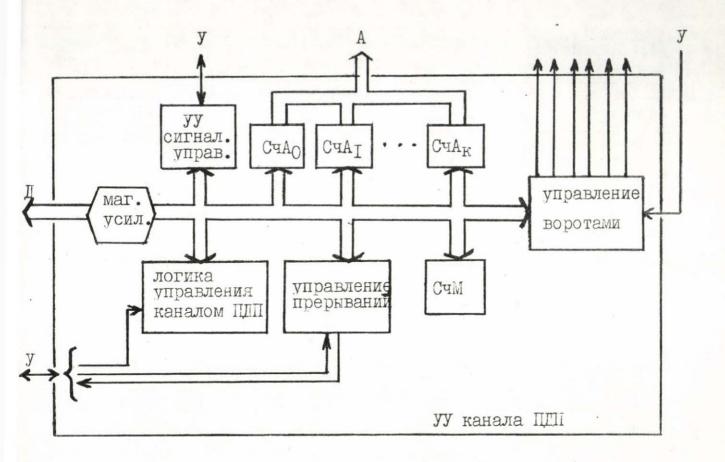

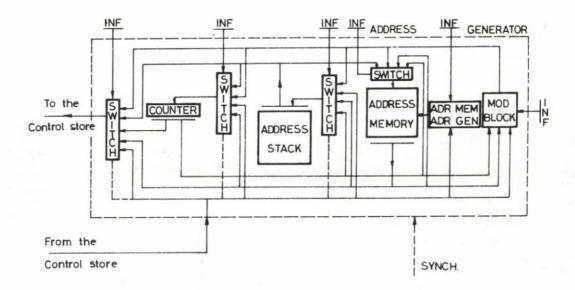

Это уу канала ПДП содержит один или несколько счетчиков длины массива, один или несколько счетчиков адресов, логику для управления сигналами шины управления и логику управления, содержащую также регистры режимов работ и состояния /см. рис. 9/.

Рис. 9. Устройство управления канала ПДП СчА — счетчик адресов СчМ — счетчик длины массива данных.

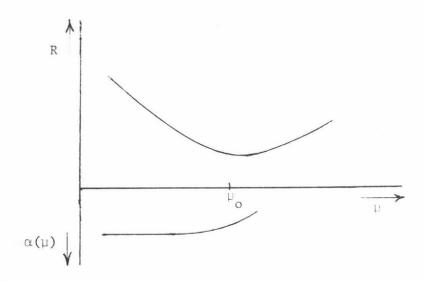

# Оценка производительности

Приведенные в пунктах 2÷4 варианты стыковки отличаются основным образом тем, в какой ширине они подключают системную магистраль микро-ЭВМ к Общей шине стыковки. Эти варианты стыковки, как видно из таблицы 1, охватывают очень широкий спектр производительности обмена данными.

Таблица 1.

| Вид стыковки                  | Режим обмена<br>данными         | Скорость обмена<br>в кбайт/сек |

|-------------------------------|---------------------------------|--------------------------------|

| T                             |                                 | 30                             |

| Последовательный<br>интерфейс | асинхронный                     | 2                              |

|                               | синхронный                      | 6                              |

|                               |                                 |                                |

| Параллельный                  |                                 |                                |